PCS 80/30

REFERENCE MANUAL

PRELIMINARY

IMSAI Manufacturing Corporation San Leandro, CA IMSAI

PCS - 80/30

REFERENCE MANUAL

Copyright 1977

IMSAI Manufacturing Corporation

14860 Wicks Boulevard

San Leandro, California 94577

Made in the U.S.A.

All rights reserved worldwide

# TABLE OF CONTENTS /

| SECTION | TOPIC                                                                                                                                                                                                                                                                                                                                                           | PAGE                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                    | 1 - 3                                                                                                                                                               |

| 11      | THE 8085 MICROPROCESSOR BOARD (MPU-B)                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

| A       | Theory of Operation  1. Introduction  2. MPU-B Circuit Description  3. 8085 Processor  4. S-100 Bus Interface  5. Status  6. Control Strobes  7. Clocks  8. Clear  9. Control Inputs  10. Interrupts  11. S-100 Bus Interface Table  12. Address Decode  13. Control Port  14. RAM  15. PROM  16. Timer  17. Parallel I/O  18. Serial I/O  19. Power Regulators | II - 3<br>II - 5<br>II - 5<br>II - 7<br>II - 7<br>II - 8<br>II - 8<br>II - 8<br>II - 9<br>II - 11<br>II - 14<br>II - 14<br>II - 14<br>II - 15<br>II - 16<br>II - 17 |

| В       | User Guide 1. MPU-B Option Jumpers 2. MPU-B Option Switches 3. Address Decoding and Control 4. Program ROM/PROM 5. RAM Memory 6. Serial I/O 7. Timers 8. Using Interrupts                                                                                                                                                                                       | II - 21<br>II - 21<br>II - 23<br>II - 27<br>II - 28<br>II - 29<br>II - 39<br>II - 47                                                                                |

| С       | Appendices 1. 8085 Instruction Set 2. Changing Option Jumpers 3. PROM Installation 4. Custom Address Decoding                                                                                                                                                                                                                                                   | 11 - 49<br>11 - 53<br>11 - 55<br>11 - 57                                                                                                                            |

| SECTION | TOPIC                                                                                                                                                                                                                                        | PAGE                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 111     | THE VIO BOARD (VIO-C)                                                                                                                                                                                                                        |                                                                |

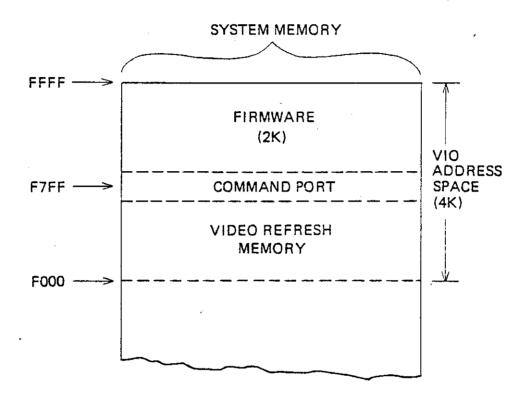

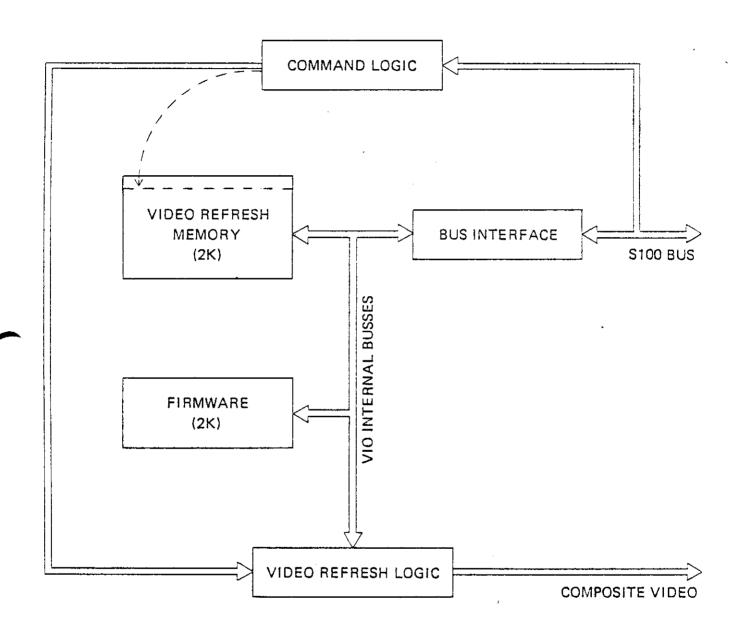

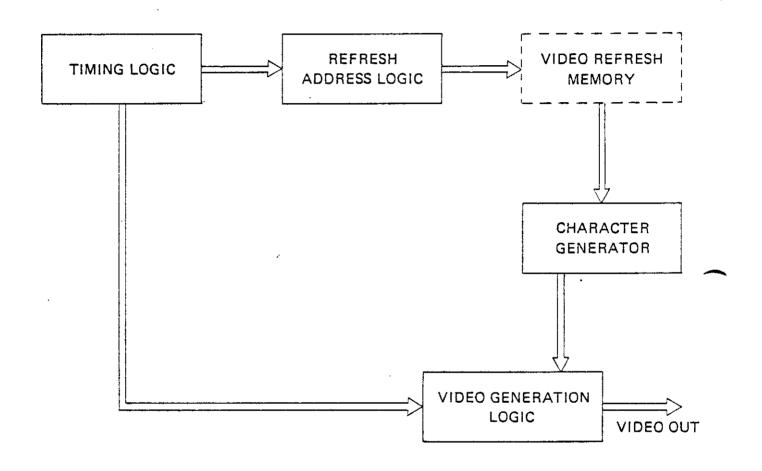

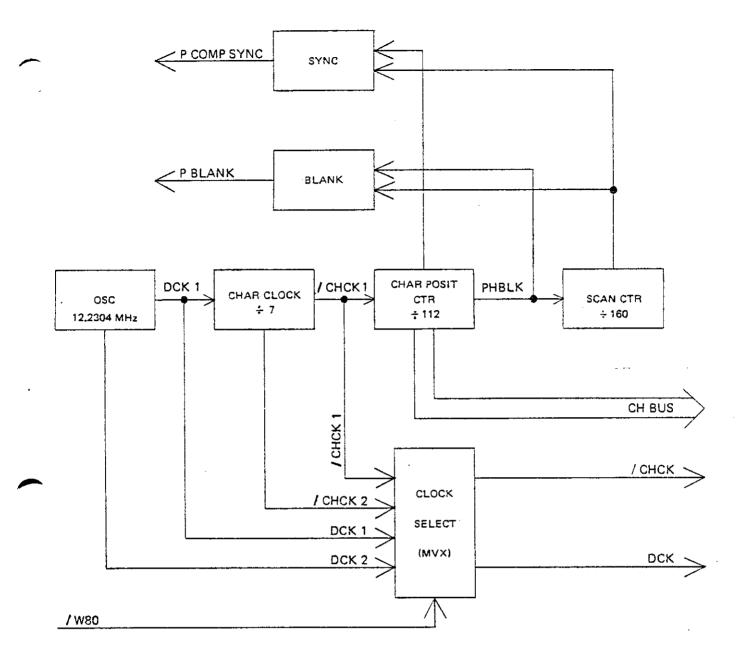

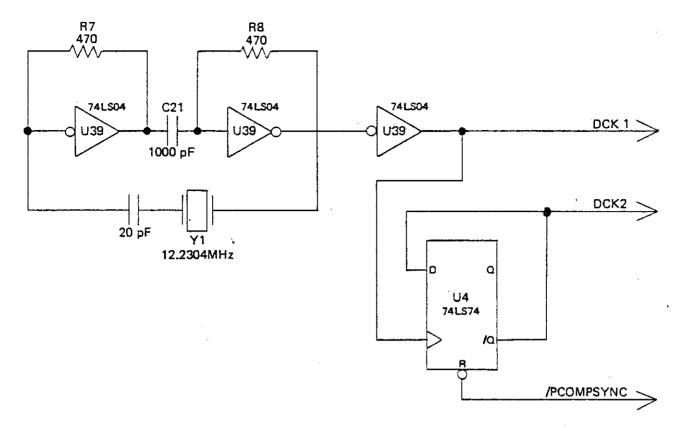

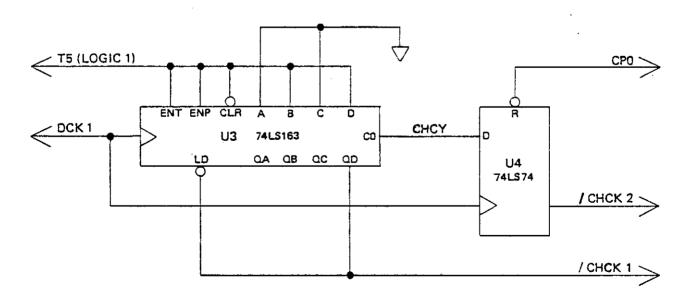

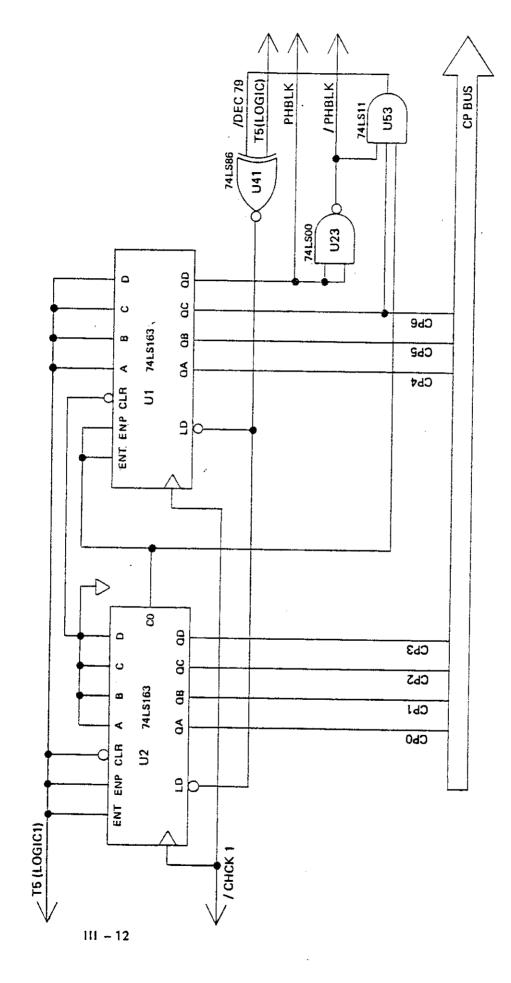

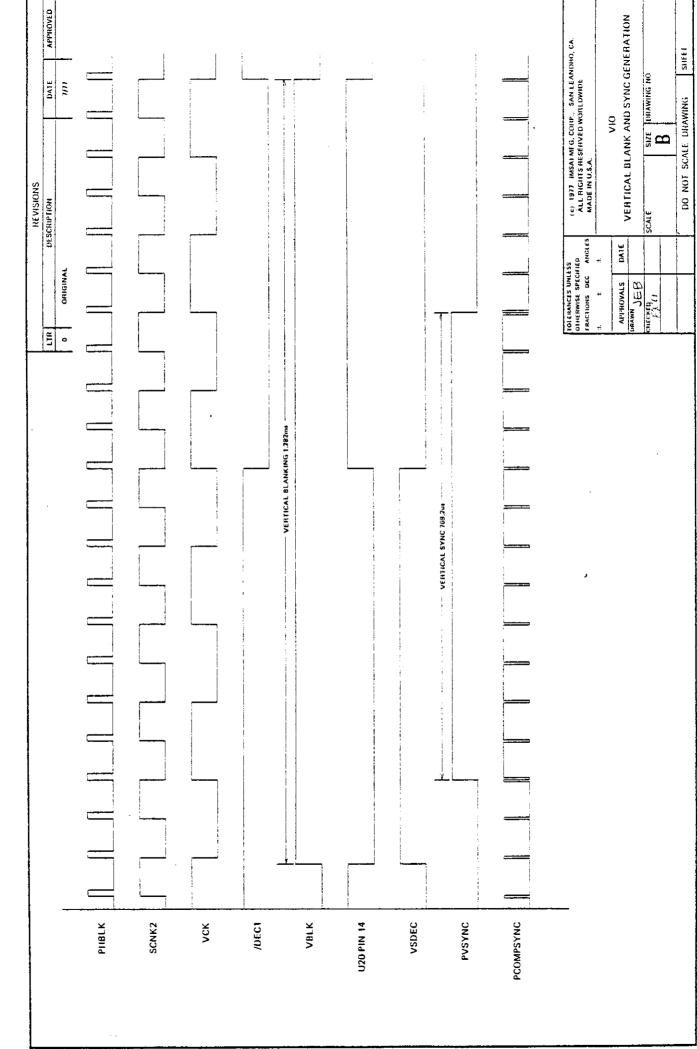

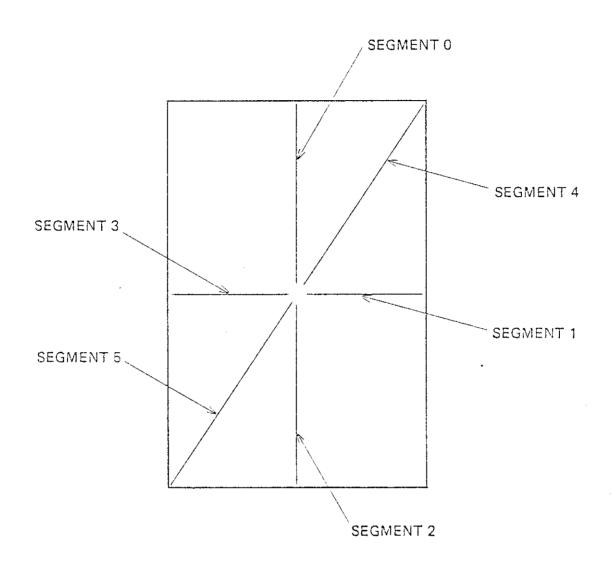

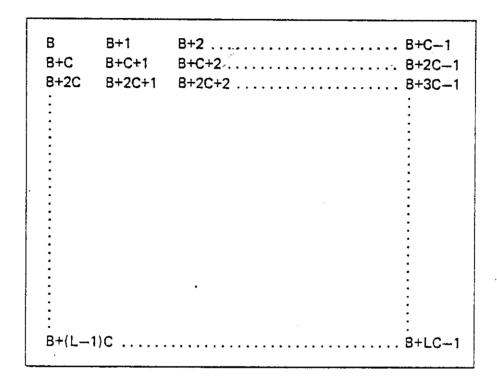

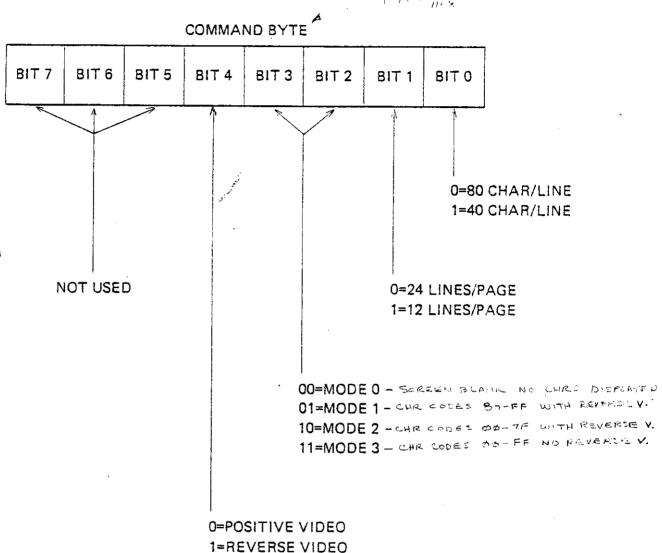

| A       | Theory of Operation  1. Hardware Overview  2. Video Refresh Memory  3. VIOROM  4. Bus Interface  5. Command Logic  6. Video Refresh Logic  a) Timing Logic  1) Dot Clock  2) Character Clock  3) Character Position Counter  4) Scan Counter | 111 - 3<br>111 - 3<br>111 - 6<br>111 - 6<br>111 - 7<br>111 - 7 |

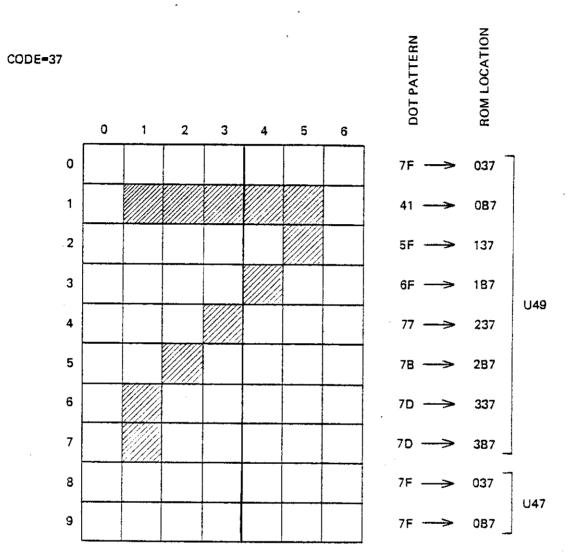

|         | 5) Sync Generation, Blanking Generation b) Refresh Address Circuitry 1)Scan/Line Counter 2)Character Address Computer c) Character Generation d) Video Generation                                                                            | III - 15<br>III - 18<br>III - 18                               |

| В       | User Guide  1. Board Configuration  2. VIO Operation with VIOROM  a) VIO Firmware  1) Screen Initialization  2) Character Display  3) Control Sequences  b) PCS-80/30 Monitor  1) Input Devices  2) Monitor Operation  3) Monitor Commands   | III - 25<br>III - 33<br>III - 33                               |

| С       | Appendices 1. Character Codes 2. X, Y Position Codes 3. Simple VIO Driver Listing 4. Programming the Character Generator ROMs/PROMs 5. Using CP/M with the IMSAI VIO Video Display Board                                                     | - 61<br>    - 97<br>    - 101<br>    - 101                     |

| SECTION | TOPIC PA                                                                                                                                                                  |                    |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| 17      | THE INTELLIGENT KEYBOARD (IKB-1)                                                                                                                                          |                    |  |  |

| A       | Theory of Operation  1. Keyboard Hardware  a) Instruction Fetch  b) Keyboard Scan  c) Display LED's  d) Speaker  e) Character Output  f) Program Lines                    | IV - 3             |  |  |

|         | 2. Keyboard Software a) Initialization b) Timer c) Speaker d) Main Loop e) Handshake f) CHECKT1 g) CHECKPROG h) CHECKSCAN i) Encoding j) Unencoded Output                 | IV - 5             |  |  |

| В       | User Guide 1. Board Configuration a) Parallel Port Configuration                                                                                                          | 1V - 9             |  |  |

|         | <ul> <li>b) Serial Port Configuration</li> <li>2. External Interface Connection</li> <li>a) Parallel/Serial Interface</li> <li>b) Parallel Interface (General)</li> </ul> | IV - 12            |  |  |

|         | <ul> <li>c) Serial Interface (General)</li> <li>3. Keyboard Operation</li> <li>a) Data Entry Mode</li> <li>b) Program Mode</li> </ul>                                     | IV - 20            |  |  |

|         | 4. External Keypad                                                                                                                                                        | IV - 22            |  |  |

| С       | Appendices  1. Parallel Handshaking  2. Control (output) Data and Handshaking                                                                                             | IV - 23<br>IV - 25 |  |  |

| ٧       | THE POWER SUPPLY (PS-28U)                                                                                                                                                 |                    |  |  |

| Α       | Theory of Operation                                                                                                                                                       | V - 3              |  |  |

I. INTRODUCTION

# . INTRODUCTION

This volume, the IMSAI PCS-80/30 Reference Manual, outlines the theory of operation of the system PC boards and contains detailed information regarding the use of the module features. Section II of the manual details the MPU-8 Microprocessor Board, Section III is a description of the Video Board (VIO-C), and Section IV relates to the Intelligent Keyboard (IKB-1). Section V contains technical information on the Power Supply (PS-28U).

II. THE 8085 MICROPROCESSOR BOARD (MPU-B)

- II. THE 8085 MICROPROCESOR BOARD (MPU-B)

- A. THEORY OF OPERATION

- 1. INTRODUCTION

The MPU-B is a central processing board for the S-100 bus based on the 8085 microprocessor. In addition to the processor, it contains:

1K program PROM/ROM 1/4 K RAM Power on jump Serial I/O Parallel I/O Timers 5-level interrupts

The 1K byte PROM/ROM socket is provided with jumpers to configure it for 1K or 2K byte PROMs or 1K, 2K, or 4K byte ROMs. A 1K ROM is included with basic system support firmware. Under software control, the ROM can be located at 0000, or at 0800. Power on clear initializes the ROM at 0000 to serve as a power on jump. The processor can write to the RAM at 0000 even when executing code in the ROM at 0000. A custom programmed PROM in this location can initialize the system, load programs in the entire 65K memory space (or more with the IMM installed), and then disable the PROM while jumping to the program start location. The PROM can be re-enabled at any time to use code stored in it, either at location 0000 or at location 0800. The PROM enable is delayed to permit a jump or call to a routine even from a program executing directly underneath the PROM location. A system reset automatically re-enables the PROM at 0000.

There are 256 bytes of RAM provided on the board for minimum stand-alone systems, and for variable & data storage at a fixed location for the loaders and monitor in ROM or custom programs in PROM. It can be software enabled/disabled, so that loader and monitor variables do not take up user memory space. It is located at DOOO, and is enabled/disabled at the same time as the PROM at D800. It is not enabled by the PROM being at 0000, however the PROM may be enabled at both locations simultaneously if the RAM is desired with the PROM at 0000.

The ROM included provides power on system initialization, automatic baud rate select if the serial interface is used, and complete monitor facilities. The monitor includes loaders for floppy disk, casette tape, and paper tape, as well as extensive machine language entry and debugging features. The monitor will automatically run from either the serial interface or a keyboard and VIO. The loaders and other routines can be called from user programs.

The serial I/O provides complete serial interfacing capability. True RS-232 levels are driven for data and handshaking lines both in computer end and terminal end configurations. No jumpering is needed. A 20 mil current loop interface is included for driving ASR-33 type devices. Baud rates are software selectible at any standard or non-standard rate up to 9600 baud in asynchronous mode, or 56K baud in synchronous mode. The input data ready, output

buffer empty, and sync detect status flags can be switched to interrupt the processor, and/or used in a polled status mode. For software compatibility, serial port addressing is the same as an MIO at 00 or 10, or both ports of an SIO at 00, or the first port of an SIO at 10.

The parallel I/O provides a complete 8-bit parallel port, with handshaking and latching available in both in and out directions. The input data ready and output buffer empty status flags can be switched to interrupt the processor, and/or used in a polled status mode. For compatibility, the connector has the same pin definitions used on the MIO or PIO, and the addressing permits a keyboard to look like the serial input of an MIO at 00, or the second port of an SIO at 10. While the parallel port is used by the monitor for keyboard input, the monitor can also use the serial port. The parallel port is otherwise free to be used for any other parallel interfaced device such as the AP-44 mini-printer.

Three 16 bit timers are provided. All three are completely software programmable and readable. They are memory mapped at D100-D103, and are software enabled/disabled along with the RAM and PROM in D000. One timer is normally dedicated to provide the baud rate clock for the serial interface, but can be used differently when serial I/O is not needed. All three timers have clock inputs of 2 MHz, with one timer's clock switch selectible to be either 2 MHz or the output of another timer. This permits a programmable interrupt or periodic interrupt period from microseconds to more than 30 minutes. Both real time clocks and time of day clocks are easily implemented. The outputs of the two timers not used for serial clock can be switch selected to interrupt the processor at count termination, or periodically, depending on the software programmed mode of operation. The timer, once programmed and started, does not have to remain enabled (with the RAM & PROM) to operate. Interrupts will occur regardless of enabled status, or it can be momentarily enabled to read the current counts. The baud rate clock continues to run with the timer disabled from memory space. The two free timers can be used to provide software controlled baud rate clocks for serial interfaces on the MIO or SIO.

The MPU-B can be used either with or without a CP-A front panel. The power on jump and monitor eliminate the need for a front panel for any program operations. A CP-A may be used for hardware development or maintenance.

All address decoding on the MPU-B is done in a fusible link ROM, so that all the specific addresses mentioned may be changed for special applications, including memory mapping the serial or parallel I/O or I/O mapping the timers or any portion of the RAM. Special monitors can be installed in the program ROM socket to support OEM applications and special applications packages. Switching the RAM, PROM, and timers out of the address space facilitates implementing larger, more sophisticated systems by removing all address conflicts.

οг

By adding power supplies and a terminal, the MPU-B forms a complete computer system with everything necessary to use it as an evaluation system or develop small machine language games or applications.

#### 2. MPU-B CIRCUIT DESCRIPTION

The IMSA1 MPU-B processor board interfaces an 8085 microprocessor chip to the S-100 bus. In addition to the processor and S-100 bus interface, the MPU-B has parallel and serial I/O, PROM/ROM, RAM, timer, and necessary address decoding. Power is regulated on the board. The processor runs at 3.0 MHz, and runs 8080 machine code along with a couple added instructions. Thus all existing 8080 code is 100% software compatible with the 8085 and MPU-B, paying due attention to the specifics of I/O device attachment. The I/O ports included on the MPU-B have been addressed such that IMSA1 software will run without any changes, at the same time allowing switch selection of either the serial port (for a terminal) or the parallel port (for a keyboard & VIO) as the system I/O device. Both serial and parallel I/O are always available for systems which use both.

Even though the processor runs 1 1/2 times as fast as a standard 8080, the S-100 bus signals have looser timing requirements due to the 8085 more efficient use of the bus. The clock lines phase 1 and 2 run at the higher 3 MHz rate, however the CLK line is run at 2 MHz for use by existing S-100 boards that depend on a 2 MHz timing source. Most other S-100 bus lines retain their old definitions. Although the timing of some of the signals is slightly different from the 8080, the chip was designed to replace 8080 in existing systems. Any properly designed S-100 boards should experience no problems running with the MPU-B.

Most of the circuitry interfaces to a local bidirectional bus, which is connected to and defined by the 8085 pins. The circuitry in each of the blocks will be described.

## 3. 8085 PROCESSOR

The 8085 processor section of the board contains only a little circuitry beyond the 8085 chip itself. A 6 MHz crystal is connected to the on-chip clock generator. All other system timing is generated from the 3 MHz clock out pin on the 8085. A power-on reset time constant of 20 milliseconds is generated by resistor PN2 and capacitor PN3 connected to the schmitt trigger reset input. The delay allows ample time for power supply voltages to stabilize before the 8085 is permitted to start running. Diode PN4 insures that if power is lost even for a short time, the 8085 will come back up running properly. When the +5 volt line falls below the schmitt's lower threshold, capacitor PN3 will be discharged quickly through diode PN4. When power is re-applied, the system begins to run only after PN3 charges to above the schmitt's upper threshold. Any manual system reset also discharges PN3, and the 8085 resumes running only after PN3 charges back to the upper threshold through PN2.

To insure that nothing connected to the bus is falsly activated during a hold or halt operation (during which the 8085 bus is three-stated), the three strobe lines (/WR, /RD, & /INTR) are held inactive by pullup resistors. The IO/M line is also pulled up to indicate an I/O status during hold or halt states, to prevent any of the on-board memory mapped circuitry being enabled, since in one mode of operation they would respond to a write strobe generated external to the MPU-B.

The 8085 is powered only by +5 volts.

The four RST lines into the 8085 have been arranged to permit use of interrupts for basic system I/O without the use of a priority interrupt card or any jumpers. One line is reserved for interrupts from a mass storage device (TRAP, @RST4.5) such as a floppy disk. The other three can be connected to the on-board I/O by activating DIP switches. The interrupts have

been segregated. RST7.5 is used for the extra timer sections, RST6.5 is used for output data buffer empty on both the serial and parallel interfaces, and RST5.5 is used for input data ready on both parallel and serial interfaces, and for sync. character detect on the serial interface. Open collector logic was used throughout the interrupt section, and jumper pads provided to connect these lines to the VIx lines on the S-100 bus. This permits connecting other interrupt devices to the same lines without a priority interrupt board. If a priority interrupt board is added, it can drive the 8 standard RST locations, and the MPU-B I/O can continue to use the RST lines unique to the 8085.

## 4. S-100 BUS INTERFACE

#### Data Out:

The local address/data bus (ADO-AD7) from the 8085 always appears on the data out bus unless an external board pulls data out disable low (/DODSBL, pin 23). It is driven by 8 sections of 8T97 three-state bus drivers.

#### Data in:

The three-state bus drivers connecting the data in bus to the local address/data bus are always held disabled unless one or the other of the two input strobes are active (/RD or /INTA). This condition is part of the definition of /IDIDSBL. These input data drivers are also held disabled by either an external board pulling data in disable low (/DIDSBL, pin 21), or by other conditions causing an active signal on internal data in disable (/IDIDSBL). /IDIDSBL is active whenever any of the on-board memory or I/O is enabled, or whenever an input strobe is not present.

## Address 0-7:

The local address/data bus is latched into PN5 at the trailing edge of ALE (address latch enable). At this time address bits 0 through 7 are on the A/D bus. The three-state driver outputs of the 8212 (PN5) drive the lower half of the address bus directly.

#### Address 8-15:

The upper half of the address bus (A8 through A15) is driven by 8T971s directly from the internal A8-A15 address bus. Both the 8T97 drivers and the 8212 drivers on the address bus can be disabled by an external board pulling address disable low (/ADDRDSBL, pin 22).

#### Data and Address Disables:

/DODSBL and /ADDRDSBL are normally driven only during a DMA transfer, when the MPU-B must be removed from the bus so that the DMA system may access the memories. Note that the address and data drivers on the MPU-B are not bidirectional; thus DMA operations to/from the on-board memory and I/O are not enabled.

#### Address timing:

Both the high and low half of the address bus appear early in T1, and since the 8212 is a gated latch, there is ample setup time to latch the full address at the trailing edge of ALE (PSYNC, pin 76) on an external card

#### 5. STATUS

Status on the 8085 is encoded differently than on the 8080. In order to generate the lines needed to run the S-100 bus, the 8085 status is used as address inputs to a ROM. The pattern in the ROM translates the 8085-type status at the inputs to 8080-type status at the outputs. The 74S288 ROM used (PN6) has three-state outputs with sufficient drive to directly run the S-100 bus. An external board can disable the status drivers by pulling status disable low (/STSDSBL, pin 18), which will remove chip select from PN6.

## Status timing:

The status appears at the same time as the address in T1, rather than having to be latched at a later time, as in the 8080. It remains valid until the corresponding time in the proceeding T1. There is ample setup time to permit latching the status with the trailing edge of ALE (PSYNC, pin 76) on an external card.

Status differences from the 8080:

Most of the status looks identical to that of the 8080 on the MPU-A. Two status lines, however, are not among the states presented by the 8085.

One of these is interrupt acknowledge (SINTA, pin 96). The 8085 does not uniquely identify an interrupt acknowledge cycle until the time that the /INTA input strobe appears. Until that time, the status is the same as an instruction fetch status. As a result, the MPU-B interrupt acknowledge status appears on the S-100 bus as an instruction fetch from the beginning of the cycle to the start of the input strobe. At that time it changes to an interrupt acknowledge status, enabling the RST or CALL op-code to be presented by the interrupting board (PIC-8, IMM, etc.). This reduces the access time available to the interrupting board to approximately 280 nsec, which is sufficient since no memory chip access time is involved.

The other status line is not decoded at all by the 8085. The stack operation status line (SSTACK, pin 98) is held not true (low) permanently (the signal can be opened should it be desired to drive it with another board). Since this line has not been used, its absence will not be a problem.

## 6. CONTROL STROBES

There are two input strobes on the 8085, which are OR'ed together and inverted to form a single positive input strobe (PDBIN) for the S-100 bus.

The 8085 signals /WR, ALE, and HLDA are used directly to drive S-100 signals (respectively) /PWR, PSYNC, and PHLDA. For systems without a front panel, the S-100 signal MWRITE is generated from /PWR and SOUT. The driver for MWRITE can be disabled by moving the dipswitch FP-/FP to the FP position (this permits the front panel to drive this line instead of the MPU-B). Provisions are also made for permanently disabling the MWRITE line for systems in which it is not used.

# Wait signal generation:

The S-100 signal PWAIT is not generated by the 8085. This signal has been used on many S-100 bus boards to generate a single wait state for memories between 500 nsec and 1 usec, so the MPU-B includes a circuit to synthesize the required timing for PWAIT. PN7 is a latch which puts the inverse of the RDY line onto PWAIT; when the 8085 is receiving a not ready signal, an active (high) PWAIT signal is put on the S-100 bus. In order to match the timing of the 8080 WAIT, PWAIT should not become true (high) until the end of T2 (beginning of TWAIT). Since RDY will normally be driven low during T1, another signal is needed to prevent PWAIT from going high too soon. PN8 is used to delay ALE at the beginning of each cycle to provide a signal to delay the start of PWAIT.

During T4, T5, and the first part of the next T1, PWAIT can return high if the memory board still returns PRDY = PWAIT. This is of no consequence since the 8085 does not test RDY during this part of a cycle.

## Control signal disable:

The five control lines will be disabled if an external board pulls control disable low (/CCDSBL, pin 19). This is normally done only during a DMA operation. If the DMA board waits for PHLDA before disabling the control bus, the 8085 will have just completed returning the strobes (PDBIN & PWR) to the inactive state. If the DMA board waits longer, or during a halt state, the MPU-B will continue to hold the strobes inactive. It is up to the DMA card to insure that the strobes cannot reach an active state during the transition of bus control.

## 7. CLOCKS

Clock out (COUT) from the 8085 provides a 3 MHz clock which is put on the S-100 phase 2 line (pin 24). This signal is inverted and used to provide phase 1 (pin 25). PN9, PN10 and PN11 form a divide by 3/2 circuit to produce a 2 MHz signal from the 3 MHz clock. The output waveform is a 2 MHz, 33% duty cycle (high) pulse train which is put on the CLK line (pin 49) for use by S-100 boards which need a 2 MHz timing source. Some S-100 boards may have originally used phase 1 or 2 for a timing source and these will need a "blue wire" change. Do not confuse the use of phase 1 or 2 as a strobe with their use as a timing source.

## 8. CLEAR

Positive going reset out (RESOUT) from the 8085 is inverted and used to drive power on clear (/POC, pin 99). The output of the driver is also used to drive external clear on the S-100 bus through a germanium diode. The diode permits a front panel, if present, to lower the external clear line (/EXTCLR, pin 54) without affecting the /POC line. With no front panel, there is no differentiation between the two clear lines.

The clock and the clear lines are driven all the time.

## 9. CONTROL INPUTS

#### Reset:

The /PRESET signal (pin 75) connects directly to the power on reset network described in the 8085 processor section. PN2 and PN3 provide enough time constant that a mechanical switch may be connected directly between /PRESET and ground, as long as the contact bounce is

shorter than approximately 10 msec.

#### Hold:

/PHOLD is held inactive by a 1K pullup, and inverted to drive HOLD on the 8085. HOLD is sampled on the trailing edge of phase 2, but does not have to be externally synchronized. The hold line is used primarily by DMA interfaces to cause the 8085 to cease executing at the end of the current instruction, and release the bus so that a DMA interface can gain control of the bus.

#### Ready:

RDY is high when both S-100 signals PRDY (pin 72) and XRDY2 (pin 12) are high. The S-100 signals are pulled inactive with 1K resistors so that they need not be driven. If they are not driven, a constant ready is presented to the 8085 and it proceeds executing at full speed.

PRDY is used by memories, I/O cards, or interrupt controllers which need to delay the 8085's sampling of input data or cause it to hold output data longer. XRDY2 is used by the front panel (if present) to hold the 8085 from continueing or to allow it to single step only. Either line pulled low will stop the 8085 between the next T2 and T3.

## 10. INTERRUPTS

The S-100 interrupts enabled line (INTE, pin 28) has no equivalent in the 8085. It is pulled true with a 1K resistor, for any interrupt boards which look at it. There should be no effect on the operation of those boards.

The interrupt request line is pulled inactive with 1K, and drives INTR on the 8085 through an inverter. There are 4 interrupt lines on the 8085 which do not exist on the 8080. Jumper pads are provided so that these may be jumpered to any of the 8 S-100 priority interrupt request lines. This eliminates the need of a priority interrupt board for up to 5 levels of interrupt; the four 8085 restart lines and the standard interrupt request. (If the interrupt request is used without an interrupt board, no one will be driving the bus at interrupt acknowledge time, and the processor will read an FF opcode, which is an RST7.

The four 8085 restart lines are pulled inactive with 1K resistors, so they need not be jumpered. Of the four, only the TRAP line (non-maskable RST 4.5) comes jumpered (to V17, pin 11). The other three can be connected to the on-board I/O via DIP switches.

## 11. S-100 BUS INTERFACE TABLE

Following is a summary of the standard S-100 bus signals including:

S-100 pin number

High true (H) or low true (L)

Driven/received by the MPU-8 (\*) jumperable (X)

S-100 signal name

```

+8 VOLTS POWER

51 - *

+8 VOLTS POWER

+16 VOLTS POWER

52 - *

2

_ *

-16 VOLTS POWER

3

Н

XRDY

53 L

/SSW DSB

4

L

VIO

54 L *

/EXTCLR

5

V11

55

L

6

L

VI2

56

7

L

V13

57

8

LX

V14

58

V15

59

9

LX

10 L X

V16

60

11

L *

V17

61

12 H *

XRDY2

62

13 H

AA15

63

14 H

AA14

64

15

H

A13

65

16 H

A16

66

17 H

A17

67

18 L *

/STSDSBL

68 H *

MWRITE

19 L *

/CCDSBL

PROTECT STATUS

69 ?

MEM. UNPROTECT

20 ?

70 ?

MEM.PROTECT

21 L *

/DIDSBL

71 H *

RUN

22 L *

/ADDR DSBL

72 H *

PRDY

23 L *

DODSBL

73 L *

/PINT

24 H *

74 L *

02 (PHASE 2)

/PHOLD

25 H *

75 L *

01 (PHASE 1)

/PRESET

76 H *

26 H *

PSYNC

PHLDA

27 H *

PWAIT

77 L *

/PWR

28 H *

PINTE

78 H *

PDBIN

79 H *

29 H *

A5

Α0

30 H *

80 H *

Α4

Al

A2

31 H *

81 H *

А3

32 H *

82 H *

A6

A15

33 H * 1

83 H *

A12

A7

34 H *

84 H *

Α9

Α8

35 H *

85

DO1

H *

A13

36 H *

DO0

86

H *

A14

37 H *

A10

87 H *

A11

38 H *

DO4

88 H *

DO2

39 H *

DO5

89 H *

DO<sub>3</sub>

40 H *

D06

90 H *

DO7

41 H *

D12

91 H *

D14

42 H *

D13

92 H *

D15

43 H *

DI7

93 H *

D6

44 H *

SM1

94 H *

D11

45 H *

95 H *

SOUT

DIO

46 H *

SINP

96 H *

SINTA

47 H *

SMEMR

97 L *

/SWO

48 H *

SHLTA

98 H *

SSTACK

49 H *

CLK (2MHZ)

99 L *

/POC

50 - *

GROUND

100 - *

GROUND

```

#### 12. ADDRESS DECODE

The address decoder on the MPU-B uses a 512x4 bit ROM (PN12), a dual 2 to 4 decoder (PN13), and several small gates. It produces chip enable signals for all the on-board memory and I/O circuits (PROM, RAM, timer, serial I/O, parallel I/O, and control port).

#### Address decode ROM:

The 9 inputs to the 512x4 rom (PN12) are the 8 high order address bits and the IO/M status line. The address decode portion of the MPU-B does not decode the low order address bits. Thus on board memory circuits either have low order address decoding at the circuit (PROM, RAM) or appear at multiple locations due to incomplete address decoding (timer). The state of address bits 8 through 15 and the I/O operation / memory operation status line (IO/M) is decoded by the ROM pattern. Since greater than 4 circuit enables are needed, the output of the ROM is encoded. The enables are divided into two groups: PROM, RAM, timer, and parallel I/O, serial I/O, control port. Output bit 4 low indicates that one of the enables in group 1 is active (PROM, RAM, or timer). Output bit 3 low indicates that one of the enables in group 2 is active (parallel I/O, serial I/O, or control port). Both bits 3 and 4 high indicate that the address and IO/M presented to the ROM are not in the address space of any of the on-board circuits. The ROM is encoded so that output bits 3 and 4 are never both low. Each of these bits is used as an enable to one half of the dual 2 to 4 decoder.

There is one time when an on-board enable may be indicated by the address and IO/M incorrectly. That is during an interrupt acknowledge. The 8085 appears as though it were going to execute the next instruction fetch at interrupt acknowledge time, except that a /INTA input strobe appears instead of a /RD strobe. In order to avoid a bus conflict and permit the interrupt board to send the interrupt op-code to the 8085, all memory and I/O circuits must recognize this condition and stay off the bus. To allow for this situation, INTA (the inverse of the /INTA strobe) is connected to the ROM chip enable input. Normally this is low, enabling the ROM; but during an interrupt acknowledge cycle, it goes high at data input time. ROM output bits 3 and 4 are pulled high by resistors when the ROM is disabled, and neither half of PN13 is enabled.

Output bits 1 and 2 are encoded to indicate which circuit enable is present, according to the following table:

| Group 1:                   |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| 21<br>11<br>10<br>01<br>00 | PROM enabled if POJM is true<br>PROM normal location<br>RAM<br>timer |

| Group 2:                   |                                                                      |

| 21<br>11<br>10<br>01<br>00 | Parallel port<br>Serial port<br>System port<br>Control port          |

In the standard ROM, group 2 is all I/O ports and group 1 is all memory mapped. The board is not restricted to this scheme, but if a different ROM is made for a custom application, some restrictions need to be considered.

Any circuit mapped as I/O cannot use the /MWRT write strobe because it is not active during I/O writes. A jumper is provided so that the two devices using this strobe (timer and RAM) can be switched to /IWR, the internal bus write strobe. If this is done, the circuits will run either memory mapped or I/O mapped, but the front panel (if present) cannot write into the memory mapped circuit since it uses /MWRT. The processor has no restrictions on writing.

The Serial I/O, Parallel I/O, and control port run from the internal strobes and can be memory or I/O mapped or both. They cannot be jumpered to respond to memory mapped writes from CP-A's. The program PROM/ROM is a read only device, and can be memory or I/O mapped. Writes to these addresses affect whatever system memory or I/O has been installed off the MPU-B. The RAM and timer can be memory mapped or I/O mapped, but if either is I/O mapped, the jumper provided must be changed to /IWR instead of /MWRT. This will prevent front panel writes to either as noted above.

When a device is memory mapped on the MPU-B, it takes up a minimum of 256 bytes of memory space. On board 1/O device decoding can be complete since the complete 1/O address appears on A8 - A15. Note that some of the 1/O circuits use address bits from A0 - A7 for further decoding of port address. In these cases the corresponding address bits in A8 - A15 are made don't care bits in the address decode ROM.

#### Dual 2 to 4 decoder:

The decoder translates ROM output bits 1 and 2 into individual enable lines according to the table above. Section one decodes group 2 (1/O and control) and is enabled only by ROM output bit 3. This group of crouits is a permanent feature of the address space of the 8085, it cannot be disabled.

Group 1 (memory and timer) is decoded by section 2. ROM output bit 4 is one of the enables for this section; the other enable input is driven by the signal IMEM. One of the four group 1 enable outputs from PN13 is not used. Instead, the output is decoded separately and ANDed with a different enable. Instead of being enabled with IMEM, it is enabled with POJM (Power On Jump Mode), and is ORed with the normal program ROM/PROM enable to provide a separate control of enabling te program ROM/PROM at this location. Typically the POJM PROM address will be 0000H to provide for system start—up. The IMEM PROM address could be anywhere, though D800H is standard. Since POJM and IMEM are program controllable, group 1 circuits can be removed from or returned to the 80851s memory space.

# Group 1:

Whenever IMEM is true, and the address is correct, the timer, RAM, or regular PROM is enabled. The timer and RAM are enabled for both read and write operations. The PROM enable is ANDed with read status in PN16, so that the PROM is enabled only during reads. During writes to the PROM's addresses, the PROM is disabled and the write occurs in whatever memory the system has installed at that address. If POJM is true, the PROM is enabled at its second location (typically 0000-07FF). Again, only PROM reads are decoded.

## Group 2:

The serial, parallel, or control port is enabled directly whenever the appropriate address is decoded. The system port output is provided with two DIP switch positions to allow it to enable either the serial or the parallel port. Only one of these switch positions should be activated at a time to avoid bus conflicts of reads from these devices. The switches allow either I/O method to be run from the same "system" port addresses so that software need not be changed when the basic I/O device is changed.

## Standard ROM addressing:

The standard addressing for the MPU-B circuits, as effected by the address decode ROM are:

Mapped as memory:

PROM @ POJM

COCOH — 07FFH

PROM normal

D800H — DFFFH

RAM

D000H — D0FFH

timer

D100H — D103H

Mapped as I/O ports:

serial 4H,5H and 12H,13H

parallel (14H,15H)

system port (02H,03H) EQUIVALENT

control port F3H

#### 13. CONTROL PORT

The control port is used to enable or disable the group 1 circuits (PROM, RAM, and timer), and the second PROM location. The second PROM location is a separate enable at a second address of the same (single) PROM chip, so that it can appear at two places (standard is 0000 at power on jump time and D800 for normal operation).

Whether the second PROM location is enabled is controled by data bit 0 in the control port. The main PROM location, the RAM, and the timer are enabled by data bit 1 in the control port. In both cases, a data bit of "0" enables the circuits, a "1" disables them. These two data bits are each latched into their own 74LS195 shift register when the control port is enabled, by putting the shift registers into load mode. The data bit is latched only into bit A, at the trailing edge of the /WR strobe. After being latched, the data bit is shifted by successive /RD or /WR strobes, until it appears at the output (QD,/QD). This takes three cycles after the control write cycle. After the output takes on its new state, it remains static because the J and /K inputs are tied to load A with QA on each shift. Internal power on clear (/IPOC) is tied to both shift registers' clear inputs, and POJM and IMEM are both taken from /QD, so that at power on time (or after any reset) all the circuits controlled by these signals are enabled.

#### 14. RAM

There are 256 bytes of RAM provided on the board, in two 8111's. The lower 8 bits of address are connected directly to the chip, along with the local bidirectional data bus. The interfacing involves no extra chips since the 8111's were designed to go directly onto a bidirectional bus. Chip select is driven by /REN from group 1 of the address decoder. The output disable pin on the memories is driven whenever either the 8085 read/write status indicates a write cycle, or the front panel (if present) drives data in disable (/DIDSBL) in preparation for a write from the front panel. The write strobe is driven by /MWRT, which is derived from MWRITE whether it is driven by the 8085 or the front panel.

If the address decode ROM addresses any of the RAM as I/O (the standard ROM does not) then the RAM write strobe should be jumpered to /IWR with the jumper provided since MWRT is not active during I/O cycles. This also prevents a front panel from writing directly into the RAM. Note: the same /MWRT - /IWR jumper affects both the RAM and the timer circuits.

#### 15. PROM

Read only program memory on the MPU-B is provided in a single ROM/PROM socket. Three jumpers are provided so that the 24 pin socket can be configured to run a 1K or a 2K prom, or a 1K, 2K, or 4K ROM. The standard chip provided is a 2K ROM with a system monitor and bootstraps.

NOTE: Care must be exercised when installing a ROM/PROM other than the one provided, since it is possible to damage some types of ROM/PROM if the jumpers provided are in the wrong position. Refer to the user's guide.

All the ROM/PROM chips were designed to attach directly to a bidirectional bus, so there is no external logic onvolved. The chip is enabled with /PEN from the address decode logic when the high-order address is appropriate.

## 16. TIMER

An 8253 chip is used as the timer circuit. No periferal gates are needed since it attaches directly to the bidirectional bus. Address lines A0 and A1 are decoded by the 8253 to select among its 4 control bytes. Since only A8 – A15 are decoded for the timer enable (/TEN), A2 – A7 are "don't care" bits in the address. As a result, the timer's 4 locations appear in multiple locations throughout the block of 256 decoded by the address decode logic. The low four locations only are called out throughout the specifications. The read strobe (/RDL) is a local read strobe generated by anding /DIDSBL with the 8085's /RD. This permits the front panel (if present) to remove the read strobe during a front panel write into the (memory mapped) timer. The write strobe (/MWRT) is derived from MWRITE, whether it is driven from the front panel or the 8085.

If the address decode ROM is changed to include accessing the timer as I/O ports, then the write strobe needs to be jumpered to /IWR at the location provided, since /MWRT does not occur during I/O writes. This will prevent the front panel from writing into the timer, even if the timer is also memory mapped at the same time. Note: The same /MWRT - /IWR jumper affects both the RAM and the timer.

The 8253 has three timers in it. Timer 0 is dedicated to providing a clock signal for the serial interface. The timer 0 out line is connected to the serial interface. Timer 0 gate is pulled high, and timer 0 clock is driven by the 2 MHz CLK2. This timer would normally be programmed to the auto-repeat square wave mode, although the system can use it for other timing functions at times when the serial interface is not needed.

Timers 1 and 2 are undedicated and available for system use. Timer 1 is clocked by the 2 MHz CLK2 line, while timer 2 can be switch selected to either run at 2 MHz, or cascaded from the output of timer 1. In the cascaded mode, the total count time of the two timers is over 30 minutes. The outputs of both timer 1 and 2 can be switch selected to cause an interrupt at terminal count (or periodically). These lines were run to RST7.5 (which is edge sensitive) to permit use of modes with short terminal output pulses. The gates on both timers 1 and 2 are pulled high.

The gate and output lines of all three timers are brought to solder-pads to permit easy modification of the board for custom applications where it is desired to drive these lines with external signals. The timers' function is not affected by whether its address decoding is enabled (IMEM). They will continue to count and produce interrupts as programmed until they are re-enabled and the mode changed. The interrupts are driven through open-collector gates so that other devices may also be connected to the same interrupt line if desired.

## 17. PARALLEL I/O

#### Data:

Two 8212's are used for the parallel I/O data path. One latches output data and drives the parallel output pins on J4 continuously. The other will buffer the input data and will also latch it if the strobe line is driven by the input device. Both the input and output data paths can use the handshaking available in the 8212, and the input data ready signal or the output buffer empty signal can both switched onto the interrupt pins for interrupt operation of the parallel port. The same two sgnals are available at the parallel I/O status port. The handshaking only runs when the respective external device drives the strobe lines. If the strobe lines are not driven, the input data ready and the output buffer empty will always indicate false. When handshaking is used, the falling edge of the strobe causes the respective status bit to go true, and latches the data on the input port. The processor's response (read or write data) causes the respective status bit to return false. The 8212 chips are selected by /KEN and A0=0, as well as the appropriate read or write strobe.

#### Status:

The parallel I/O status port is implemented with four sections of a 74LS367 to drive the internal data bus, and some gates to enable the 3-state buffers with /KEN=0 and A0=1 and /RDL=0, which is during the read strobe to the port address decoded at the address decoding. The output port output buffer empty signal is connected to data bit 0. The input port input data ready isconnected to data bit 1. These are the same bits as the respective status signals from the 8251 serial interface chip, to simplify software drivers which run both devices. Also driven during parallel status reads are two upper data bits. Bit 7 is driven with IMEM, and bit 6 is driven with POJM. These two bits are high when the respective on-board functions are enabled. This permits interrupt routines to determine the state of the board so they can return correctly.

#### Power:

Ground, +5 voits regulated, +18 voits unregulated, and -18 voits unregulated are provided on the parallel 1/O connector. The +5 voit regulator was designed to be able to supply up to several hundred milliampers of power to the parallel connector, however it should be realized that any power drawn results in higher dissipation at the regulator. If too much current is drawn or to little ventilation provided, the +5 voit regulator may shut itself down.

#### Connector:

The parallel I/O connector is a 26-pin dual-row header, suitable for; connection to flat cable connectors. The pin definitions result in the same signal/wire connections as used in the MIO. Pin 26 is unused to permit the use of 25 wire cable and D type 25 pin connectors at the rear of the cabinet. The schematic shows the 26 pin connector pin-numbers in the arrow boxes, and the 25 pin connector pin-numbers in the circles. These pin numbers assume the standard pin numbering for D type connectors, standard flat cable pin numbering for the 26 pin connector (so that the flat cable wires counted from the edge correspond to the pin numbers), and a cable wired to connect pin 1's.

# 18. SERIAL I/O

The serial I/O port uses an 8251 serial interface chip. This USART will support asynchronous or synchronous serial communications to 9600 or 56000 baud respectively. It is interfaced to standard EIA RS-232 levels and pins for providing either the computer or terminal end of a serial line. It also will drive an ASR-33 Teletype type 20 mil. current loop interface. The output buffer empty and the input data ready or sync. detect status bits can be switched to drive the interrupt lines.

The 8251 is connected directly to the on-board bidirectional bus. A0 drives the command/data input, the other 7 address bits are decoded at the address decoder to form /SEN. The clock input is driven with 2MHz, and power on clear and on-board read and write strobes drive the appropriate inputs.

The EIA RS-232 signals from the USART (including RTS, CTS, DTR, DSR, R and T Data, R and T synchronous clocks) are connected to the serial I/O connectors through RS-232 receivers and drivers. DIP switches permit selecting the on-board receive clock for asynchronous mode, or an off-board clock for synchronous data mode. DTR and CTS inputs are tied true with resistors to eliminate the need for jumpers when they are not driven. Carrier detect is tied true.

The current loop interface will switch and sense a 20 mil. loop compatible with the ASR-33 Teletype. The loop current source is provided, and any other current source should be removed. The current loop connections must not be referenced to ground. Provision for filtering the input data is made to permit reliable operation of the typically noisy ASR-33.

# Serial connectors:

There are two serial I/O connectors on the board. They are both 26 pin dual row connectors suitable for flat cable connection to the EIA standard D type 25 pin connectors. Assuming a cable wired so that pin 1's on the two ends are connected, the 26 pin connector pin-numbers are indicated on the schematic in the arrow boxes, and the EIA standard RS-232 pin numbers

are indicated in the circles. The two connectors are arranged so that one is configured as a computer end of an RS-232 line, and the other is configured as a terminal end. Depending on the use of the system, the cable from the RS-232 line should be plugged into one connector or the other, with no jumpers being necessary. The board is not designed to use both connectors at once.

The current loop connections are made to the computer end connector only. If for some reason it is desired to operate in current loop mode as a terminal, a custom cable can be made to effect the proper connections.

Since the S-100 bus does not include a chassis ground, the chassis ground line from the RS-232 connectors is terminated in a .040<sup>st</sup> pin socket. If it is desired to connect this line at the board, a wire with a .040<sup>st</sup> pin can be attached to the chassis, and plugged into this socket.

#### 19. POWER REGULATORS

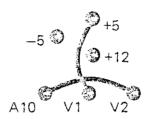

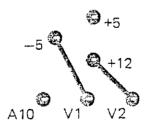

Plus and minus 12 volts for the RS-232 drivers, pullups, and the PROM/ROM are regulated by TO-220 style three terminal regulators. They regulate only a small amount of current, so they are heat-sunk on the foil on the board. Minus 5 volts for the PROMs is regulated by another TO-220 regulator in series with the -12 volt regulator, to more evenly distribute the heat dissipation.

The plus 5 volt regulator is a TO-3 style three terminal regulator, mounted on a heatsink. It is required to supply the 5 volts for this board, plus any additional current taken by an external device connected to the parallel I/O port. The MPU-B 5 volt current drawn is typical 1.3 amps, maximum 1.6 amps.

Tantalum capacitors are provided at the inputs of each regulator for stability, and .1 uF ceramic bypass capacitors are provided throughout the board among the logic chips.

IMSA1 PCS-80/30 SECTION II-B MPU-B USER GUIDE

## B. USER GUIDE

In this section we describe how to set up and use your MPU-B processor board. The level of detail is intended to supply the assembly language system programmer and OEM user with all the information needed to use the board. There are several option jumpers which must be changed if you are going to operate the MPU-B differently than set-up at the factory. You will probably not want to change these jumper options. There are a number of switch-options for functions which are often set differently in separate systems. These should be checked before operation to insure that the desired mode of operation is enabled. If your MPU-B has arrived as part of a factory-assembled system, it will be set-up to run. In that case you may wish to delay referring to the option set-up portion of this chapter until you wish to change the factory settings.

For normal operations, an operating system program, a high-level language, or an applications program is loaded into the computer from mass storage. The procedure for initializing the system and loading the desired program is described in the Sections IV and V of the PCS-80/30 User Manual. The option selection and machine-language operation of the MPU-B board only is described here. This section is primarily of use to those programming in Assembly or machine language, and during initial installation.

# 1. MPU-B OPTION JUMPERS

Some of the options provided on the MPU-B will be used only in special situations, such as when a system is being customized for a special configuration or special application. These options have been provided as jumper-pads on the printed-circuit board, and they have a small trace on the board connecting these pads in the standard factory configuration. Unless you have a special situation, you will not need to set or change these jumpers.

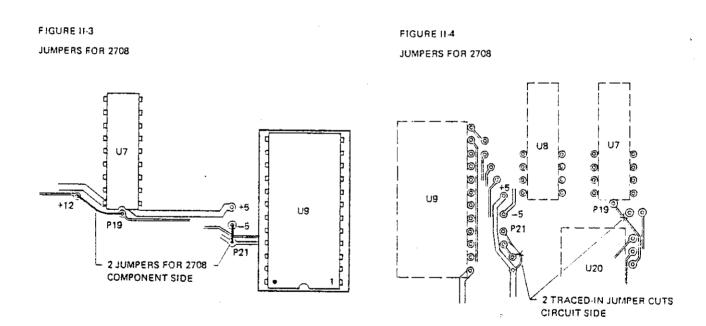

Three of these jumpers allow configuring the MPU-B program ROM socket to accept different Assembled boards are jumpered at the factory for the ROM installed. Other options are described in the Program ROM/PROM section. Note: INCORRECT JUMPERS CAN DAMAGE THE ROM, refer to the appendix on PROM installation.

There are jumpers to remove bus drive from the signals SSTACK, INTE, and MWRITE. These jumpers appear on the schematic but are not described since they are primarily for factory use. Should a knowledgeable user wish to change one of these and need information, he should contact the factory.

A .040" pin socket is provided for connecting RS-232 line AA (chassis gnd.). Solder pads for wires or pin sockets are provided for 8085 signals SID and SOD, as well as timer signals GATE and OUT for all three timers.

Jumper pads permit connecting any of the eight vectored interrupt lines on the bus to any of the four restart inputs or the interrupt request line on the 8085. The standard configuration is described in the USING INTERRUPTS section (II-B,8).

## MPU-B OPTION SWITCHES

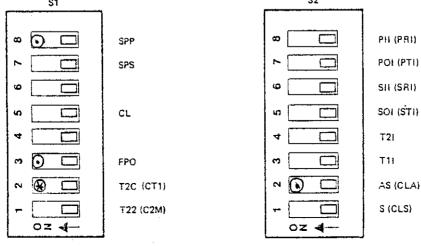

All the options which might normally be changed are provided with switch positions to enable the board to be quickly and easily configured as desired. A brief description of the switches is provided here for reference.

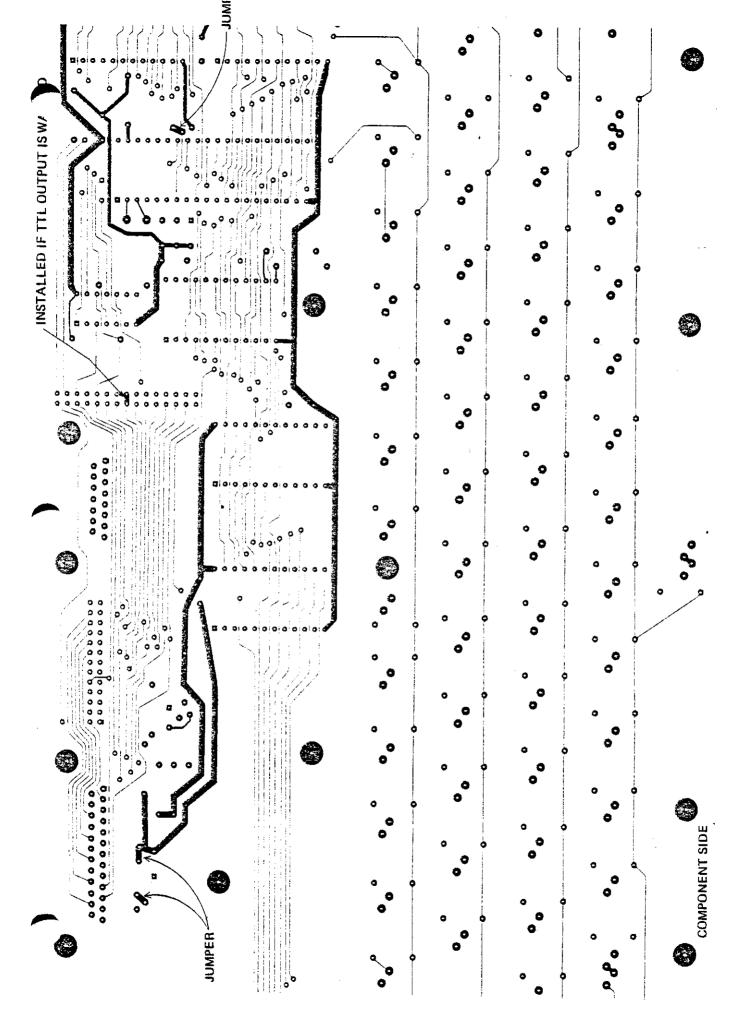

SHOWS CONFIGURATION AS DELIVERED. SMITCHES ON FIGURE II -1 Ð CHANGE - KLV SWITCH LOCATIONS TOP OF BOARD \$2 S1 m PH (PRI) SPP

IMSAI PCS-80/30 SECTION 11-B MPU-B USER GUIDE

#### **OPTION SWITCHES**

SYSTEM PORT SERIAL ENABLE >> SYSTEM PORT PARALLEL ENABLE

(SPS IN/QUI)

Only one of this pair of switches should be enabled at a time. They cause either the serial or parallel I/O port (or neither) to respond to the system port addresses (02 data, 03 status). (They will continue to respond to their standard port addresses.) If both switches are disabled, then ports 00 through 03 are unused, permitting an external I/O board (such as an MIO) to be installed using the bottom 4 ports.

∠ ASYNCHRONOUS CLOCK ENABLE (CLA IN/OUT)

SYNCHRONOUS CLOCK ENABLE (CLS IN/OUT)

Only one of this pair of switches should be enabled at a time. One of these must be down to enable use of serial receive. They connect either the internal band rate clock (for asynchronous mode) or an externally generated clock signal (for synchronous mode) to the USART's receive clock input.

CURRENT LOOP ENABLE

(CL IN/OUT)

If current loop operation is desired, the CL switch should be enabled. If synchronous mode is to be used, then the CL switch should be disabled.

SERIAL TRANSMIT BUFFER EMPTY INTERRUPT SERIAL RECEIVE CHAR. READY INTERRUPT

(STI IN/OUT) (SRI IN/OUT)

Neither, either, or both of these may be enabled as desired. The first will cause an interrupt to occur (RST6.5) whenever the serial I/O transmit is enabled and the transmit buffer is empty. A jump to the interrupt service routine must be located at 0034H. The second will cause an interrupt to occur (RST5.5) whenever the serial I/O receive is enabled and a character is waiting to be input to the processor. A jump to the interrupt service routine must be located at 002CH.

PARALLEL TRANSMIT BUFFER EMPTY INTERRUPT PARALLEL RECEIVE CHAR. READY INTERRUPT

(PTI IN/OUT) (PRI IN/OUT)

Neither, either, or both of these may be enabled as desired. The first will cause an interrupt to occur (RST6.5) whenever the parallel I/O output buffer empty status is true (set by handshake strobe). A jump to the interrupt service routine must be located at 0034H. The second will cause an interrupt to occur (RST5.5) whenever the parallel I/O input data ready status is true (set by the same strobe which latches data). A jump to the interrupt service routine must be located at 002CH.

IMSA I PCS-80/30 SECTION II-B MPU-B USER GUIDE

TIMER 1 INTERRUPT ENABLE (T11 IN/OUT)

TIMER 2 INTERRUPT ENABLE (T21 IN/OUT)

Neither, either, or both of these may be enabled as desired. Each switch will cause an interrupt to occur (RST7.5) when its respective timer output goes low (terminal count or 1/2 terminal count depending on programmed mode). A jump to the interrupt service routine must be located at 003CH. Timer 0 is the baud rate generator, and does not connect to the interrupts. Note that RST7.5 is an edge triggered interrupt, so that timer modes which produce a terminal pulse may be used without danger of missing the interrupt.

TIMER 2 CLOCK 2 MHz ENABLE (C2M IN/OUT)

TIMER 2 CLOCK T1 OUT ENABLE (CT1 IN/OUT)

Only one of these two switches should be enabled at a time. One or the other must be down to provide a clock input to timer 2. When the first one is enabled, timer 2 counts at a 2 MHz rate (2 million counts/second). With the second switch enabled, timer 2 increments one count at each high to low transition of the output of timer 1. Cascading the timers this way and enabling only timer 2 interrupt permits extended periods to be timed without software intervention.

FRONT PANEL INSTALLATION (Panel IN - FP1)

(Panel OUT - FP0)

This switch must be placed in the enabled position in any system with a CP-A installed, and must be placed in the disabled position in any system without a CP-A. Even when temporarily inserting a front panel for maintenance, this switch should be moved to IN. Note that the sense of IN and OUT is reversed from the other switches.

#### 3. ADDRESS DECODING AND CONTROL

There are six circuits on the MPU-B which appear in the memory or 1/O space of the processor. They are:

- 1 Firmware ROM

- 2 256 byte RAM

- 3 Three TIMERS

- 4 8 bit parallel I/O port

- 5 Serial I/O port

- 6 MPU-B control port

Some of the six circuits can appear in multiple (redundant) locations in memory or I/O space. Some can be made to appear/disappear from memory space using the control port.

For descriptive purposes, the functions are divided into three groups according to how the sections are enabled/disabled by the control port. The allocation of memory - 1/O space to these six functions is as follows:

IMSA1 PCS-80/30 SECTION II-B MPU-B USER GUIDE

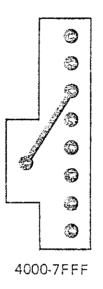

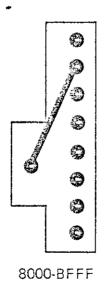

| GROUP | BYTES | FUNCTION ADI                  | DRESS     |

|-------|-------|-------------------------------|-----------|

| 0     | 2K    | ROM for system initialize     | 0000-07FF |

| 1     | 2K    | ROM for monitor functions     | D800-DFFF |

| ì     | 256   | RAM for monitor variables     | D000-D0FF |

| 1     | 4     | TIMERS & serial clk.          | D100-D103 |

| 7     |       | RESERVED do not use           | D104-D7FF |

| 2     | 2     | PARALLEL I/O                  | 14-15     |

| 2     | 2     | SERIAL I/O                    | 12-13     |

| 2     | 2     | SERIAL I/O                    | 0405      |

| 2     | 2     | SYSTEM PORT for SER. or PAR.  | 02-03     |

| 2     | 1     | CONTROL PORT for address mode | : F3      |

The four digit numbers refer to hexadecimal memory addresses, and the two digit numbers refer to hexadecimal port addresses. The ROM in groups 0 and 1 is actually the same ROM which can appear at two different locations. The serial and parallel I/O can also appear at multiple locations.

## CONTROL PORT AND SOFTWARE MEMORY CONTROL

The MPU-B control port is a single I/O mapped port address (F3). It is a write-only port and only two of the eight data bits are active. The two bits control whether group 0 or 1 circuits appear in the memory space or not. When they are 0, the circuits appear in the memory space; when they are 1, the circuits do not appear in the memory space and whatever memory is installed in the system at that location then appears.

# Control port:

Group 0 control: bit 6

BIT 6 = 0 2K ROM appears at 0000-07FF

BIT 6 = 1 System memory (as installed) appears at 0000-07FF

Group 1 control: bit 7

BIT 7 = 0 2K ROM appears at D800-DFFF

256 byte RAM appears at D000-D0FF TIMERS appear at D100-D103

BIT 7 = 1 System memory (as installed) appears at D000-DFFF

# CONTROL PORT DEFAULT AND SWITCHING RESTRICTIONS:

At power on time and at any reset, control port bits 6 and 7 are both set to 0 so that the firmware ROM, RAM, and timers are all enabled. The two control bits operate independently, and there are no restrictions on acceptable combinations. Either group may be enabled or disabled at any time or sequence desired. The control bits are changed with an out F3.

IMSAI PCS-80/30 SECTION II-B MPU-B USER GUIDE

If a read is attempted from the control port, the resulting data will be FF. Due to the logic implementation, this will also result in both groups 0 and 1 being disabled. That is, a read from the control port is equivalent to a write with data bits 6 and 7 equal to 11s.

#### CONTROL PORT EFFECT:

When the 2K ROM is enabled, all memory reads from those locations read from the ROM. Thus the program in the ROM can be executed. All memory writes from those locations, however, will succeed in writing data to the system memory (if installed).

Both the RAM and timers are read/write devices. When they are enabled, all memory reads and writes from those locations are from/to the RAM and timers. During the time they are enabled, no access is possible to system memory at those locations.

The combination of devices and addresses labeled group 1 above cannot be enabled/disabled separately. They can only be switched in and out as a group. As a result, when group 1 is enabled, system memory from D800-DFFF is accessible for writes only, and system memory from D000-D7FF is not accessible at all.

When group 0 (firmware ROM) is enabled, system memory at COOO-O7FF is not accessible for reads, since reads now come from the firmware ROM. Writes, however, are not restricted from system memory at all by group 0 being enabled. If group 1 is disabled to remove its write restrictions, group 0 can be enabled and still permit writing to the entire 65K memory space. Thus a loader or other system initialization routine executed from the firmware ROM can load/initialize the entire memory as needed.

#### POWER-ON LUMP

When the MPU-B is run without a front panel, it will come up running starting at location 0000 at power-on time or reset time. Since the firmware ROM defaults to being enabled at the same time, the MPU-B will begin to execute the code stored in the ROM at 0000. The code contained in the ROM can range from a disable group 0 and jump to monitor sequence, to a complete automatic system initialize and load from external mass storage, ending with a disable firmware ROM and jump to system start.

The factory installed ROM functions vary for assembled systems. The ROM with kits or assembled boards sold separately is the same as that supplied with the PCS-80 system model 30 unit. The factory installed ROM can be 1K bytes or larger, depending on the system.

## CONTROL PORT ENABLE / DISABLE TIMING:

When either group 0 or 1 is either enabled or disabled by program control, there is a 3 CYCLE DELAY before the commanded change in status takes place. This is to allow for a 3-byte instruction fetch, such as a jump or call, before the ROM appears/disappears. If a 3-byte instruction is not desired, the programmer must take precautions to allow for the status change being delayed 3 cycles. The delay is for 3 true 8085 cycles, and is not affected by any DMA cycles which may occur during this time. Interrupt cycles, however, will be counted, so if the 3-byte instruction is in 0000-07FF or D800-DFFF, then the programmer needs to insure that no interrupt will occur. Otherwise the instruction fetched will not be what the programmer

## expected.

Example of a POWER-ON JUMP to location E000

| ROM<br>ADDR. | CONTENT |        | Notes:                                                                                                                                                                                             |

|--------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000         | MVI     | A,0C0H | Get byte to turn off group 0 and 1 Output byte to control port Jump to location E000 (Group 0 and 1 will both become disabled after reading all the jump and before the fetch following the jump.) |

| 0002         | OUT     | F3     |                                                                                                                                                                                                    |

| 0004         | JMP     | E000   |                                                                                                                                                                                                    |

## CONTROL PORT STATUS

The current status of the group 0 and 1 enable can be read by the processor. It appears in the status byte from the parallel port, bits 6 and 7. A 0 indicates enabled, and a 1 indicates disabled. The capability to read this status permits a system to use interrupt routines which can sense the system status, modify it as necessary to service the interrupt, and return it to its original state before returning. The function of the status bits is the same as the function of the control bits. A status read from the parallel pot address followed by an output of the result to the control port will result in no change.

# MEMORY STATUS SENSE (in parallel I/O status byte)

| Bit 6 = 0 | ROM at 0000 enabled                                                  |

|-----------|----------------------------------------------------------------------|

| Bit 6 = 1 | System memory 0000-07FF enabled                                      |

| Bit 7 = 0 | ROM at D800 enabled<br>RAM at D000 enabled<br>Timers at D100 enabled |

| Bit 7 = 1 | System memory D000-DFFF enabled                                      |

## SERIAL and PARALLEL I/O PORT ADDRESSING

The parallel port is always accessible at I/O port 14 (data) and I/O port 15 (status). If the option switch SPP (System port parallel) is enabled, then the parallel port also appears at I/O port 2 (data) and 3 (status). When it is enabled at both locations, accessing it by either set of addresses or a mixture of the two produces identical results. For example, it would make no difference if data was written to port 02 or port 14, whether the status was read from port 03 or port 15.

The serial port is always accessible at 1/O port 12 (data) and 1/O port 13 (status) as well as always available at 1/O port 04 (data) and 05 (status). If the option switch SPS (System pi serial port also appears at 1/O port 02 (data) and 03 (status). As in the parallel port, there is no differentiation between the multiple ports at which it may be accessed.

IMSA1 PCS-80/30 SECTION 11-B MPU-B USER GUIDE

The port addresses 12,13,14,15 are the same configuration of data and status as would be presented by an SIO 2-2 board addresses at 10H. The port addresses 02,03,04,05 are the same configuration as an SIO 2-2 board addressed at 00.

The typical consol I/O addresses for IMSA1 software are 02 and 03. The MPU-B permits switching either the serial port (for a terminal) or the parallel port (for a keyboard to be used with a video display) to respond to these locations. A serial device is expected at ports 04 and 05 by some IMSA1 software. New firmware intended for the MPU-B alone would use the permanent addressing at 12,13,14 and 15.

# 4. PROGRAM ROM / PROM

The firmware ROM supplied with the MPU-B will vary for different systems. For details of functions included in the ROM, the appropriate USER MANUAL should be consulted. For boards purchased separately, the ROM included is that used in the PCS-80 model 30. It provides system initialization and loaders with a limited monitor.

For a system modified for a special application, the firmware ROM may be replaced with a PROM or a ROM containing firmware to support that application. This would be done if the system was not going to be used as a general purpose machine, but rather for only the special application. Since complete system initialization, load, and error recovery can be put in the PROM, special application systems may be easily made which involve no operator actions other than the power switch to begin operation.

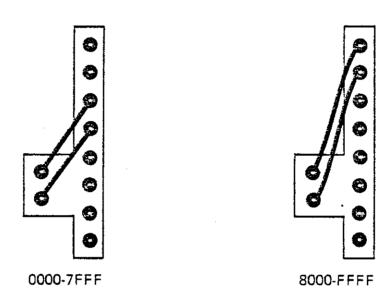

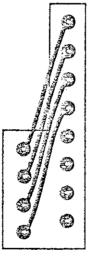

Jumper options permit the use of 1K (2708 type) or 2K (2716 type) Eraseable PROMIs, and also 1K, 2K, or 4K ROMIs for systems produced in higher quantities.

CAUTION: Factory jumpers have been installed for the ROM supplied. Other PROM's or ROM's may be DESTROYED if installed without changing the jumpers. Refer to Appendix 2.

When a 1K PROM/ROM is installed without changing the address decode ROM, it occupies 2K of memory space. It will appear in both the upper and lower halfs of the 2K space reserved for the 2K ROM. If a 4K ROM is installed, the address decode ROM must be changed in order to permit access to the upper half of the 4K ROM. Contact the factory for details.

## ADDRESSING:

The ROM/PROM can appear in two locations. It will appear at 0000 when group 0 is enabled (see CONTROL PORT section above). It will also appear at D800 when group 1 is enabled.

This is not two different ROM's, but rather it is the same ROM appearing in two different locations. It can appear at both simultaneously if both groups 0 and 1 are enabled. In that case a read from 0000 will get the same data as a read from D800. A read from 01E4 will get the same data as a read from D9E4, etc.

IMSAI PCS-80/30 SECTION II-B MPU-B USER GUIDE

The programs run from each area (0000-07FF and D800-DFFF) must share the space in the ROM. The program running in 0000-07FF will need to be at the bottom of the ROM to start properly at location 0000 at power-on time. A program running in the D800-DFFF area would then be ORG¹ed at D800 plus the length of the program at 0000.

For example, a system initialization and boot from floppy disk routine may take 140H bytes. It would be ORG'ed at 2000 and placed in the bottom 140 bytes of the ROM. A set of standard utilities can then be put in the ROM to run at the upper location. It would be ORG'ed at D940H and could extend up to DFFF. It would be placed in the ROM following the initialization and boot routine.

The ROM may be used at either location at any time, but the two locations have different facilities. Running from only 0000 permits a routine to have WRITE access to the entire 65K memory space of the 8085 for complete system initialization. Loader variable storage is limited to the registers in the processor or reserved system memory, however. When running from D800-DFFF, WRITE operations are restricted from D000-D7FF, but 256 bytes of RAM are available (D000-D0FF) which are not part of the system memory and are switched out when the ROM is switched out. For a routine needing complete access as well as larger variable storage, it is possible to run the routine at 0000-07FF, enable the RAM / upper ROM location before variable access, and disable the RAM / upper ROM location before accessing system memory at D000-DFFF.

## 5. RAM MEMORY

There are 256 bytes of read/write memory on the MPU-B, which can be enabled or disabled as part of group 1 circuits. When it is enabled, it is at D000-D0FF. The upper part of the RAM area is used for variable storage by the monitor program in the ROM, and the rest of the RAM area is free for user storage or programs. If the monitor is not to be used, nor any routines called in the ROM, then the entire 256 bytes may be safely used.

If the RAM has been disabled (through the control port), then it is not available for use until re-enabled. While it is disabled, whatever memory is loaded into the system at that location responds to the processor; when it is enabled, the memory in the system at the RAM address is disabled and the RAM on the MPU-B responds to the processor. Any time the program enables or disables the RAM, there is a 3 CYCLE DELAY before the status change takes place, to allow for a jump or call if desired. The RAM is enabled/disabled along with the other functions located in DXXX. Its enable is not separable.

Information is not lost in either the 256 bytes of RAM or in the system memory it blocks as the program enables or disables it. At power up time or on reset, the RAM is enabled.

## 6. SERIAL I/O PORT

The MPU-B has a serial I/O port implemented with an 8251 USART. Both synchronous and asynchronous operation are possible. It is configured to allow both current loop and RS-232 operation with no jumper changes. The baud-rate clock is obtained from a TIMER section under software control. For details on the clock generation, see the TIMERS section (II-B,7).

#### CURRENT LOOP

The current loop interface provides 20-mil current loop including the current source. It is suitable for ASR-33 teletypes and devices with similar interfaces.

The MPU-B current source is referenced to ground. The interface to which it is connected must be isolated from ground to avoid possible damage.

The normal internal configuration for an ASR-33 teletype is with no current source and isolated from ground. However, it is possible that a unit would be jumpered to provide a current source. Before connecting a unit to the MPU-B, it should be checked to insure that the interface lines are isolated from ground. This can be done easily by measuring the resistance between the interface lines and the chassis in the ASR-33. A standard VOM is adequate, and the resistance measurement should indicate an open circuit.

The MPU-B current loop interface operates full duplex. The ASR-33 jumpers should be configured for full duplex if they are not already configured that way.

## DIRECTIONS FOR JUMPERING

There is a terminal strip located at the right rear of the Teletype (ASR33). The terminal strip is behind a panel of square white plastic connectors and also connects to the TTY power cord. The terminals are numbered from 1 to 9. The connections required between the MIO and these terminals are shown in Table II-1. In addition to making these connections, it may be necessary to perform the following operations on your Teletype.

- Full Duplex Operation Move YEL/BRN wire from Terminal 3 to Terminal 5 and move WHT/BLU wire from Terminal 4 to Terminal 5.

- 2. Change receiver current level from 60 ma to 20 ma; move V10 wire from Terminal 8 to Terminal 9.

- 3. Change current source resistor to 1450 ohms. Locate the current cource resistor in front of the power supply and move the BLU wire to the tap labeled 1450.

TABLE II-1 CONNECTIONS FOR ASR-33

| Signal Name        |    | 25 Pin EIA<br>Connector |   |

|--------------------|----|-------------------------|---|

| Current Loop Out + | 20 | 23                      | 7 |

| Current Loop Out - | 24 | 25                      | 6 |

| Current Loop In +  | 8  | 17                      | 3 |

| Current Loop In -  | 22 | 24                      | 4 |

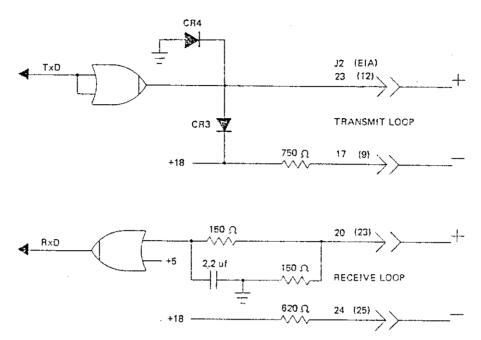

FIGURE II 2 CIRCUIT FOR CONNECTIONS TO ASR-33

The serial interface lines are brought to the rear of the cabinet through a flat cable to a standard 25 pin D type connector. The MPU-B end of the cable should be plugged into either J2 or J3. The current loop pins on J2 are configured the same as those on the SIO board, while the current loop pins on J3 are configured the same as those on the MIO board. On J2, the current loop pins are numbers 9 (+) and 12 (-) for the output loop, and numbers 25 (+) and 23 (-) for the input loop. An external cable should connect these pins to the ASR-33, attaching the wires according to the diagram above. On J3, the corresponding pins are 23 (+) and 25 (-) for output and 17 (+) and 24 (-) for input. Unless a cable wired for the MIO current loop pin configuration is already available, it is suggested that the SIO configuration on J2 be used.

# **OPTION SWITCHES**

To run current loop, option switch CL must be in the enabled (IN) position. Current loop mode may only be used with asynchronous mode, for which switch CLA must be enabled, and switch CLS must be disabled.

## RS-232