#### UCRI BOARD

### FUNCTIONAL DESCRIPTION

The September, 1975 "Computer Bits" column in <u>Popular Electronics</u> proposed a standard for the recording on magnetic tape of hobbyist's digital information. The column included a description of the proposed standard (known as the Hobbyist Interchange Tape System), circuitry to interface the tape recorder and digital system, and a listing of sample programs to drive the interface. The IMSAI UCRI Board provides the hobbyist this circuitry and all necessary logic to control the interface from the 8080 system bus. The only additional hardware required to read or write information is an audio-quality tape recorder and 2 patch cords with RCA phono jacks.

Tri-state buffer drivers and low power Schottky TTL circuits are used for completely 8080-bus-compatible plug-in interface. The UCRI Board requires one Mother board slot, and occupies one I/O port address. Jumper options permit the user to select any one of the 256 possible addresses.

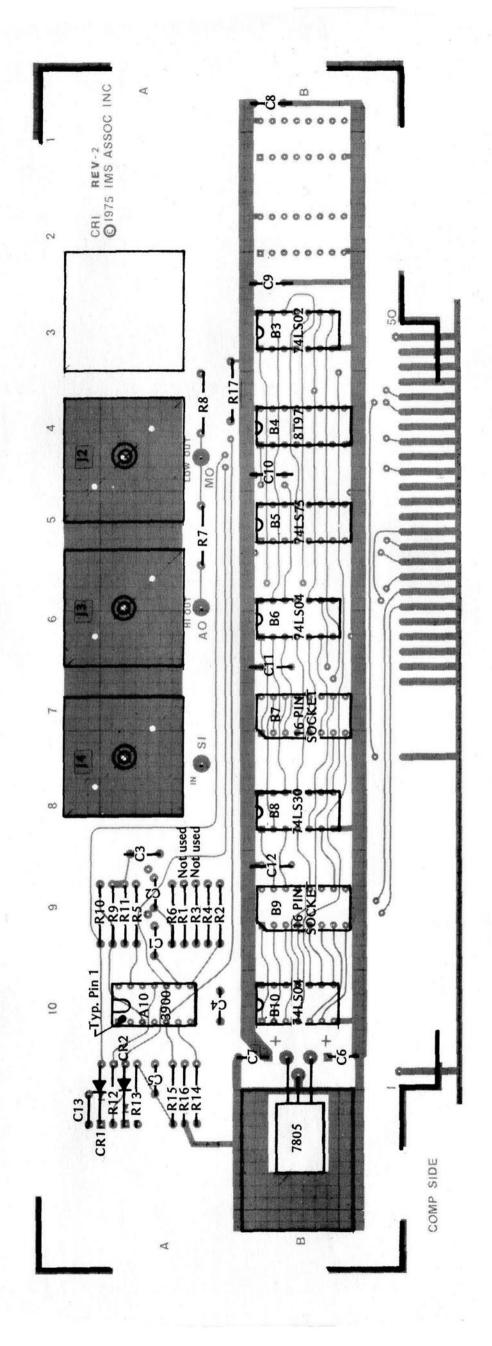

Physically, the board measures 3" x 10" and connects to the computer with a standard 100 pin edge connector. An on-card voltage regulator with current limiting and high-quality tantalum by-pass capacitors are included.

For further details of the HIT Digital Recording Standard and system, please refer to the September, 1975 <u>Popular Electronics</u>, pages 57-61. You will note that our circuit and software are slightly different than PES because we found that theirs had a few problems.

UCRI Board Rev. 2

Theory of Operation

Edition 2

#### THEORY OF OPERATION

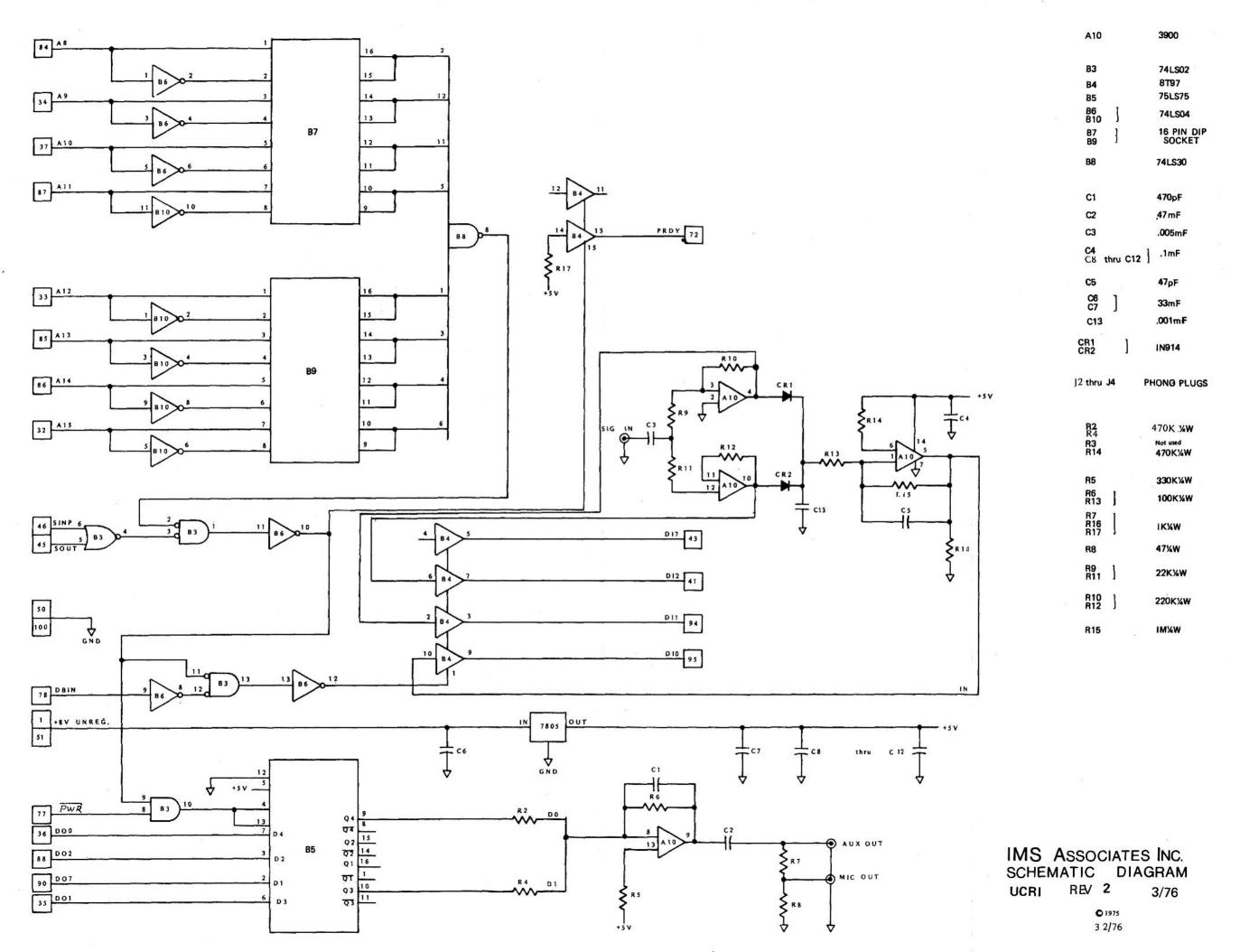

The UCRI board is a direct implementation of the circuit published in the "Computer Bits" column of the September 1975 issue of <u>Popular Electronics</u>, with the additional logic needed to run this circuit from the IMSAI 8080 system.

The interface circuit published uses the LM3900 Quad-Op amp with Norton current sensitive inputs. (See the enclosed notes). The output circuit uses one section of the LM3900 as a buffer amplifier with a gain of approximately 2/5ths and an integrating capacitor to reduce the response to higher frequencies, thus rounding the corners of the square waves produced by the program through the output bits 0 and The signal is then fed to the output jack to the tape recorder through a DC blocking capacitor and stepped down to a lower level to permit connection to a microphone input with a resistive divider. Square waves are put out by alternately outputting bits 0 and 1 as both 1's. 0's. When the signal is stopped, bits 0 and 1 should be written as one "1" and one "0", to give an intermediate output level. This gives a wave form as illustrated.

The input section of the interface uses the remaining three sections of the LM3900. Two of the sections are used as inverting gain-of-10 and non-inverting gain-of-10 amplifiers to buffer the signal. With the proper input voltage levels, one member of this amplifier pair will saturate and chip on the positive going peak of the signal, and give 0 volts output during the negative-going peak. The other member of this pair does the same but with the opposite peaks; it also inverts so that both outputs are positive. A diode is connected from each of these sections to the input of the third section, which is connected with positive feedback as a Schmitt trigger, to produce approximately a square wave at the output.

This square wave will be high if either of the 2 previous amplifiers' outputs are high; thus, if a tone signal is present, the Schmitt trigger output will be high except for the very brief moments that the signal crosses through zero. Cl4 acts as a filter and holds the Schmitt input on for these short periods, insuring a constant high output from the Schmitt trigger. Of course, if the tone input

UCRIBoard Rev. 2

Theory of Operation

Edition 2 ?

ceases, C14 discharges and the Schmitt output falls; thus, the input circuit produces a l (high) output during the time it receives a tone input, and a 0 (low) output when it receives a blank spot of tape.

To interface this circuit to the 8080 system, the UCRI board's logic must recognize the proper address and enable the board. The board is enabled when properly addressed (74LS30 output low) and either of the signals SINP (STATUS INPUT) or SOUT (STATUS OUTPUT) is high. The inputs of the 74LS30 (B8) are determined by the selection of the address jumper wiring in positions B7 and B9.

When these conditions are met, the PROCESSOR READY line is enabled (via B4, Pin 13) and held high to indicate no WAIT cycles are necessary. If the processor strobes the DBIN (DATA BUS IN) line, the input bit from the Schmitt trigger is put on the DATA IN bus, while if the processor strobes the WR line, the 7475 latch stores the data on the DATA OUT bus and presents it to the UCRI board's input circuitry.

A 7805 voltage regulator powers the UCRI board circuitry and by-pass capacitors are used to eliminate any high-frequency noise from the power bus.

### Notes on Norton Current Op-Amps

For those unfamiliar with Norton Current Amplifiers, it should be noted that the current-sensitive inputs are different from the inputs in most integrated circuit operational amplifiers in that they are sensitive to current rather than voltage. Thus while a normal integrated circuit Op-amp can have a common mode voltage, and input currents are always extremely low, the LM-3900 op-amp always has an input voltage of approximately 0 volts, and it can have a common mode current.

One of the clearest circuits to indicate the difference between the Norton input operational amplifier and a conventional input operational amplifier is the non-inverting amplifier used to clip the signal from the audio tape recorder. This is the section using pins 11 and 12 as inputs and 10 as the output.

UCRI Board Rev. 2

Theory of Operation

Edition 2;

If this operational amplifier were the conventional type, the input currents would be extremely low and, therefore, the voltage drop across both the 22K input resistor to Pin 12 and the 220K feedback resistor to Pin 11 would be approximately 0 volts, because of the very low current.

The negative feedback loop would cause the operational amplifier to adjust its output voltage to equal the input voltage and the circuit would perform as a one-to-one voltage follower. However, with a Norton input operational amplifier, both inputs are always held at approximately ground potential, thus the current through the 22K ohm resistor is 10 times as great as that through the 22OK ohm resistor for the same voltage. In other words, if one has 1/10th of a volt at the input producing a current into Pin 12 of the operational amplifier through the 22K ohm resistor, one needs one full volt at the output to produce the same current through the 22OK ohm resistor into the negative input of the amplifier in order to balance the inputs according to current levels.

Thus, with a Norton Input Amplifier with input sensitive to current levels, this circuit produces an amplification factor of 10.

IMS Associates Inc. ASSEMBLY DIAGRAM CR-I REV. 1 12/75

| Ĵ |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

UCRI Rev. 2

Parts List

Edition 2

| BOARD | • | CRI |

|-------|---|-----|

|       |   |     |

| Part #        | <u>Quantity</u> | Description                                 | Identifying Marks   |

|---------------|-----------------|---------------------------------------------|---------------------|

| 741S02        | 1               | Quad 2 Input NOR (Low<br>Power Schottky)    | SN74LS02N           |

| 741S04        | 2               | Hex Inverter (Low<br>Power Schottky)        | SN74LS04N           |

| 741S30        | 1               | 8 Input NAND (Low<br>Power Schottky)        | SN74LS30N           |

| 741S75        | . <b>1</b>      | Quad Bistable Latch<br>(Low Power Schottky) | SN74LS75N           |

| 7805          | 1               | 5 V. Positive Voltage<br>Regulator          | MC7805CP            |

| 3900          | 1               | Quad Op Amp                                 | LM3900M             |

| 1N914         | 2               | Silocon Diode                               | ln914               |

| 8 <b>T</b> 97 | 1               | Hex Tri-State Buffer                        | N8T97B              |

| DC47          | 1               | .47uf Disk Capacitor                        | .47M                |

| DC005         | 1               | .0luf Disk Capacitor                        | 5K                  |

| DC001-16      | 1               | .00luf Disk Capacitor                       | .001P or 1000P      |

| DC-47P        | 1               | Disk Capacitor                              | Z5U 47M             |

| DC-470P       | 1               | Disk Capacitor                              | Z54970M             |

| DC1-30        | 6               | Disk Capacitor                              | .1 or 104           |

| H-HSTO-220    | 1               | Heat Sink                                   | Thermalloy/6106B-14 |

| H-RCA         | 3               | RCA Phone Jack                              |                     |

| ICH-16        | 2               | Integrated Circuit<br>Header                | Numbered 1-16       |

| PC- UCRI      | 1               | Printed Circuit Board                       | UCRI                |

UCRI Rev. 2 Parts List Edition 2

| Part # Ou  | antity | Description                       | Identifying Marks    |

|------------|--------|-----------------------------------|----------------------|

| R-47-1/4   | 1      | 47 Ohm, 1/4 Watt Re-<br>sistor    | Yellow/violet/black  |

| R-1K-1/4   | 3      | lK Ohm, 1/4 Watt Re-<br>sistor    | brown/black/red      |

| R-22K-1/4  | 2      | 22K Ohm, 1/4 Watt Re-<br>sistor   | red/red/orange       |

| R-100K-1/4 | 2      | 100K Ohm, 1.4 Watt Resistor       | brown/black/yellow   |

| R-220K-1/4 | 2      | 220K Ohm, 1/4 Watt Resistor       | red/red/yellow       |

| R-330K-1/4 | 1      | 330 K Ohm, 1/4 Watt Re-<br>sistor | orange/orange/yellow |

| R-470K-1/4 | 3      | 470K Ohm, 1/4 Watt Resistor       | yellow/violet/yellow |

| R-1M-1/4   | 1      | lM Ohm, 1/4 Watt Re-<br>sistor    | brown/black/green    |

| STS-16     | 2      | Solder Tail Socket                | 16 Pin Socket        |

| TC-33-25   | 2      | Tantalum Capacitor                | 33-25                |

| s/n/lw     | 8 ea.  | 5/16" screw/nut/lockwasher        |                      |

| s/n/lw     | 1 ea.  | 1/4" screw/nut/lockwasher         |                      |

8" piece hook-up wire

solder

paper tape 1

#### ASSEMBLY INSTRUCTIONS

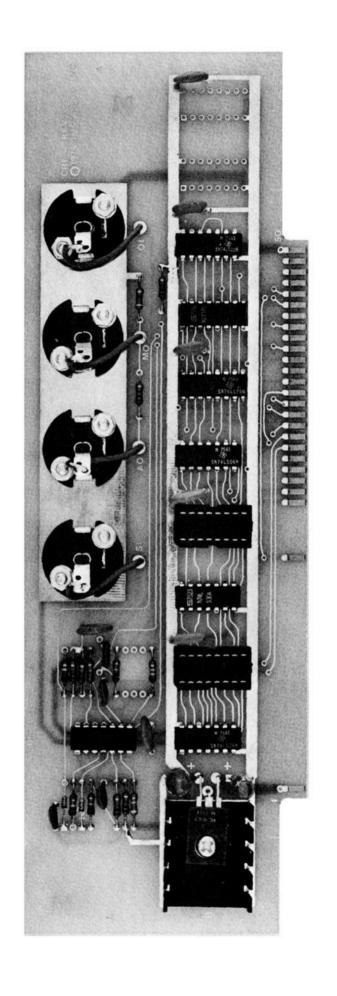

Begin assembly by inserting the 15 resistors into the proper locations on the board. Verify proper values and positions, and solder. (Note: Resistors Rl and R3 are omitted, leave these spaces empty). Next, insert the two 1N914 Diodes (CRI, CR2). Check to be sure the cathode (banded end) is oriented as shown (toward the square pad), and solder. Insert the seven integrated circuits; check for proper location, bent pins, and correct orientation (Pin 1 towards top of board, away from edge connector). Solder the seven IC's.

Install the six .1 uf by-pass capacitors and the other five ceramic disc capacitors. Check for proper values and locations, and solder them in place. Fasten the 7805 and heat sink (with #6 screw, lockwasher, and nut), and solder the 7805 in place. Install the two .33 uf tantalum by-pass capacitors; observe polarity (+ to +), and solder.

The RCA phone jacks should now be inserted into the appropriate holes and fastened with #6 screws, lock-washers and nuts.

Short wires should now be run from the pads on the board (SI, AO, MO) to the center connectors of each of the RCA phono jacks The 16-pin sockets should be inserted and soldered in locations B7 and B9 and the board is now ready for use.

UCRIBoard Rev. 2 User Guide Edition 2

### USER GUIDE

The UCRI board user should refer to the <u>Popular Electronics</u>

Article about the <u>HIT</u> system. The circuit published in that article is reproduced exactly on the UCRI board with the addition of the logic necessary to interface the circuit to the 8080 system. The user must select a board address (see Jumper Socket instructions) and provide the software to run the UCRI board.

DATA OUT BITS 0 and 1 (DO 0, DO1) are used to create the recording signal. The software routine should write out a square wave (equal time of both 1's and both 0's) at approximately 2000 Hz on these bits. While it was suggested by Popular Electronics to use another data bit as an "envelope" to control the 2000 Hz square wave, we have found it works better to control the square wave in software. In order to leave the output signal at 0 volts when the square wave is stopped, bits 0 and 1 should be written as one "1" and one "0".

To write to tape, connect the tape recorder's Auxillary or Mic inputs to the appropriate UCRIboard jacks. The presence of the 2000 Hz square wave will write a tone into the tape, while the absence of the square wave will write a blank onto the tape.

To read from tape, connect the recorder's output jack to the SIGNAL INPUT jack of the UCRI Board. The presence of the tone on tape will produce a l signal (high) on INPUT BIT 0, while the presence of a blank spot of tape will produce a 0 (low) on INPUT BIT 0. If this bit is always read as a l, then the hook-up should be checked for excessive noise or hum which may be causing the receive circuit to always indicate the presence of a signal. The UCRI Board provides 4 output bits and 4 input bits so that should for any special purpose the user desire to output or input more bits of information, such as to turn a recorder on or off, the capability is already built into the board. All that is needed is the interface between the TTL levels provided and the function desired to be controlled.

UCRIBoard Rev. 2 User Guide Edition 2

The traces presently on the board\* are arranged so that all 4 bits input to the same section of the LM3900. Using binary weighted values of resistors for R1, R2, R3 and R4 will result in a 4-bit digital to analog converter; permitting arbitrary 16-level wave shapes to be created by software and output to an audio system. We suggest the values:

|    |                | Controlled By |

|----|----------------|---------------|

| R3 | 500K or 470K   | Bit 3         |

| Rl | 1.0 M          | Bit 2         |

| R4 | 2.0 M          | Bit l         |

| R2 | 4.0 M or 3.9 M | Bit 0         |

The circuit can also be used for the more recent Byte Magazine-sponsored audio cassette data interchange standards. A software routine can be written which will output either 8 cycles of 2400 Hz or 4 cycles of 1200 Hz as required for mark or space bits. The filter circuit will properly condition these signals for recording with no changes at all. However, the receive circuit must now detect whether the signal from the recorder is above or below 0, rather than detect just the presence or absence of a signal. With this recording standard, there is always a signal and what is detected is the frequency of this signal. If the software routine could sense at any given instant whether the signal was above or below 0, then software timing loops could then determine whether it was changing at a 1200 or 2400 Hz rate.

To achieve this function, the input circuit may be used in either of two ways. For the first modification, remove diode CR2 and capacitor Cl3. The signal on INPUT BIT 0 will now be a square wave of the same frequency as the recorded tone. Software could determine this frequency, and subsequently decide if the data is a 1 or a 0. This is the preferred modification for using the Byte standard.

<sup>\*</sup>Rev. 2; earlier revisions can be easily modified to do this by cutting (R3 & R4) free of (A10 pin 13 & R5); then connecting (R3 & R4) to (R1 & R2 and A10 pin 8 and R6 & C1).

UCRI Board Rev. 2 User Guide Edition 2

Alternatively, the second method may be used. Pin 4 will be high during positive swings of the input, while pin 10 will be high during negative swings. These points are connected to data in bits 1 and 2 on the board, producing complementary "0's" and "1's" readable by the software. These inputs, however, have not gone through a Schmitt Trigger so that the signals will not be as well defined as the bit 0 signal. By detecting simultaneous zero crossing (the two signals are complements), software is again able to determine the frequency, hence value, of the recorded data. This modification leaves the UCRI board to function normally and, also, has fair noise immunity due to the simultaneous zero-crossing detection scheme.

Listings of basic routines to run both types of recording follow.

UCRI Board Rev. 2 Board Addressing Edition 2

# BOARD ADDRESSING

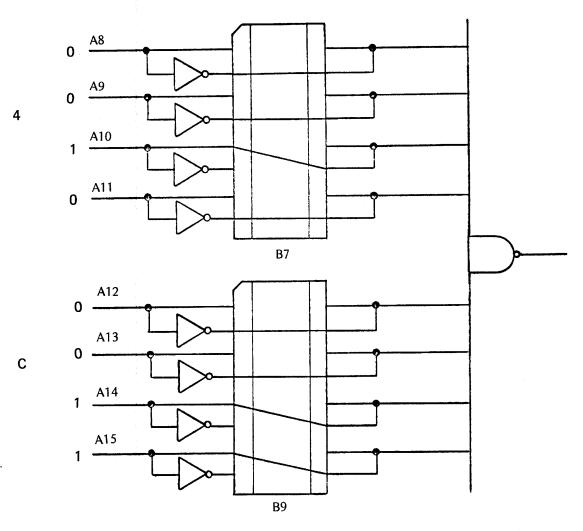

Positions B7 and B9 contain the user-jumpered 16-pin address selection sockets. These jumpers allow the UCRI board to respond to any 1 of the 256 possible I/O port addresses.

As shown on the schematic, to enable the UCRI board it is necessary to have all eight inputs to the 74LS30 (B8) high. The user should select the desired address and then jumper the address selection sockets so that when that address appears on address lines A8 through A15, all the NAND inputs are high, and the board is then enabled.

UCRI Board Rev. 2 Board Addressing Edition 2

Socket B7 controls lines A8 through All while socket B9 controls lines Al2 through Al5. Each socket contains values of 4 lines and 4 line complements. If the user-selected address presents a 1 on an address line, that line should be directly connected to the NAND input via a short wire jumper on the socket header. Conversely, if the user selected address presents a 0 on an address line value should be connected to the NAND.

It is suggested that for lines jumpered to enable on a l value that the jumpers be placed diagonally across the socket (i.e., Pin l to Pin l5) and for lines jumpered for a 0 value, the jumper be placed straight across the header (i.e., Pin 2 to Pin l5). This convention allows easy visual determination of the selected address, for l's appear as diagonals and 0's as horizontals. An example of a correctly jumpered socket pair for the address C4 hex or 304 octal is shown above.

If desired, very frequent address changes may be easily implemented through the exchange of an 8 pole dip switch for each socket.

All 8 of the NAND inputs should be jumpered to respond to either a 1 or a 0. While any input left unconnected will appear to act as a 1, open inputs are very susceptible to noise pulses.

### **UCRI SOFTWARE**

### INTRODUCTION

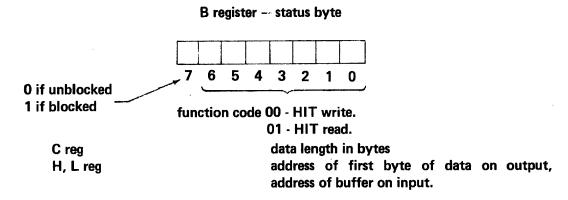

The UCRI software package is designed to perfectly compliment the highly general nature of the IMSAIUCRI board. A highly modular design allows the easy insertion of additional new standards as they arise. Provision is made for both blocked and unblocked records. The user has complete freedom to include error checking and recovery within the blocked format. Revision 0 of the software package is supplied with the necessary modules to handle the HIT (PE) standard. The BYTE standard will be available shortly.

### **CALLING SEQUENCE**

The UCRI software resides at 1500 hex. It has one entry point, at 1500 hex. When called, it expects the following information in the registers:

On return, CARRY is cleared, unless an error accurred while reading in blocked mode. If CARRY is set, the A-register contains a code indicating the type of error.

| CODE | ERROR                               |

|------|-------------------------------------|

| 1    | No initial sync characters formed   |

| 2    | More than 32 sync characters formed |

| 3    | No STX character found              |

| 4    | No ETX character found              |

A typical calling sequence to write a blocked record at 100 Bytes starting at location 1200 hex would be:

| MVI  | B, 80H   | get code for blocked write |

|------|----------|----------------------------|

| MVI  | C, 100   | get count                  |

| LXI  | H, 1200H | get address of date        |

| CALL | 1500H    | go write it                |

|      |          | return here                |

# **DATA FORMATS**

HEADER

In unblocked mode, the specified number of bytes are copied from memory directly to the tape with no formatting.

In blocked mode, the data is preceded with a header and followed by a trailer. The exact format of each block is as follows:

TDAILED

| HLADLI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INAILEN |        |              |                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|--------------|--------------------|

| A commence of the commence of |         |        |              |                    |

| 32 sync characters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | STX     | length | DATA         | ETX Error<br>Check |

| 32 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 byte  | 1 byte | 256 byte max | 1 byte 2 bytes     |

| The fields are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |        |              |                    |

### The fields are:

| SYNC Field    | 32 SYN characters (16 hex). Used to make sure the software is synchronized with the data. |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| STX           | A "Start-of-Text" (02 hex) character.                                                     |  |  |  |  |

| <b>Length</b> | The length of the Data filed in bytes.                                                    |  |  |  |  |

| Data          | The data copied from memory                                                               |  |  |  |  |

| ETX           | An "End-of-Text" (03 hex) character                                                       |  |  |  |  |

| Error Check   | Currently not used. Reserved for error checking.                                          |  |  |  |  |

It is recommended that blocked format be used, as it results in better reliability than unblocked.

# **OPERATING SEQUENCE**

When writing to the tape, the following sequence should be employed:

- 1) Rewind the tape.

- 2) Start the tape recording, wait at least 10 seconds to make sure the plastic leader has cleared the record head.

- 3) Start the program.

- 4) When the program is done, wait a few seconds before stopping the recorder.

When reading from the tape, this sequence should be employed:

- 1) Rewind the tape.

- 2) Start the program.

- 3) Start the tape reading.

- 4) When the program is done, stop the recorder.

|  |  |  | ~           |

|--|--|--|-------------|

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |

|  |  |  | <del></del> |

|  |  |  |             |

|  |  |  |             |

|  |  |  |             |