## GENEBAUMGARUNCK

DIGITAL COMPUTER REPS. 155 SAN LAZARO AVE. SUNNYVALE, CA 94086 (403) 245-4460 (415) 327-2327

#### INTRODUCTION

System 2400 is a 24-bit general purpose systems oriented digital computer which provides extensive computing capability in a low cost processor of advanced design. It is ideally suited to a wide range of digital applications where performance, reliability, programming efficiency, and cost effectiveness are of prime consideration.

NOV 1 9 1974.

STANDARD FEATURES - The basic sytem 2400 central processor incorporates a number of standard features normally available only as separately priced options. Included in the list of standard features are:

- Memory Protection

- · Memory Parity

- Priority Interrupt System

- Power Fail Detection

- Real Time Clock

- Cabinet Enclosure

MEMORY - The main memory is a 750 nanosecond 24-bit ferrite core memory with standard byte parity checking. The basic memory size of 8192 24-bit words is modularly expandable to 32768 words in 8192 word increments. The 2400 CPU is pre-wired to accept the maximum memory configuration without additional mainframe hardware.

ADDRESSING - All of memory is directly addressable by each single word memory reference instruction. Programming problems inherent with paged addressing schemes are eliminated on the System 2400 computer.

REGISTERS - Four general purpose programmable registers are provided, three of which may be used for indexing. All memory reference, shift, and input-output instructions may be indexed using any of the three index registers.

INSTRUCTIONS - The System 2400 instruction set includes 100 basic commands organized into six instruction classes: Memory Reference, Immediate, Shift, Input-Output, Register-Register, and Control. Significant features of the instruction set include:

- Hardware Multiply and Divide

- Double Precision Arithmetic

- Signed 16-Bit Immediate Instructions

- Variable Shift Instructions

- Immediate, Word, and Double Word Comparsion Instructions

- Conditional Branching Instructions

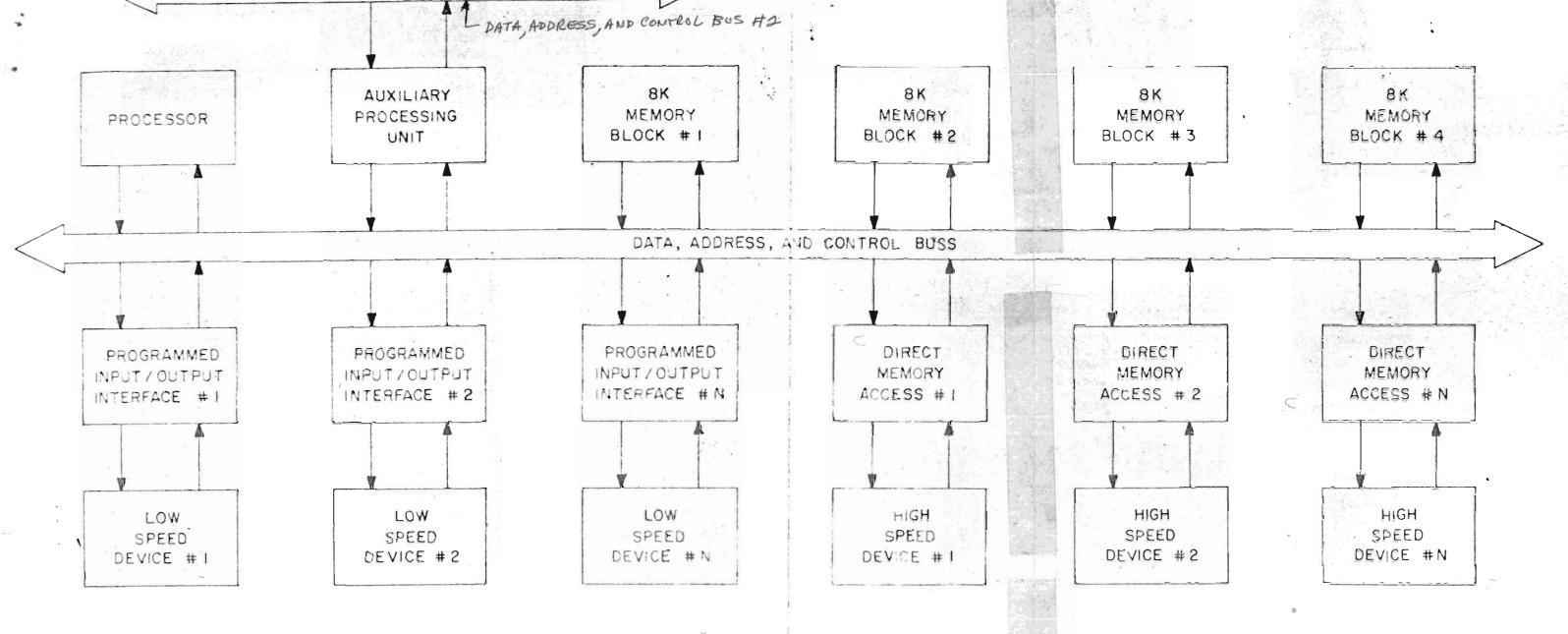

INPUT-OUTPUT SYSTEM - The input-output system is organized around a multiple access buss structure that allows direct communication between two input-output devices, an input-output device and the main memory, the CPU and an input-output device, or the CPU and main memory. Buss priority is determined during each memory cycle resulting in a maximum latency time for high priority direct memory access input-output requests of 750 nanoseconds. The input-output system provides for byte or word transfers under program control and high speed block data transfer under direct memory access control. The basic input-output system is pre-wired to accept up to eight programmed I/O (PIO) controllers and up to five direct memory access (DMA) controllers. Block transfer rates of up to 32 million bits per second are possible under DMA control.

PRIORITY INTERRUPT SYSTEM - The basic System 2400 processor accepts up to 255 external interrupt signals. The priority interrupt system provides a fully nested interrupt structure with automatic source identification by hardware. Assignment of interrupt priorities is flexible and completely independent of the input-output system. Interrupt priorities may be reassigned without requiring corresponding modifications to the input-output addressing structure. The interrupt structure is specifically organized to facilitiate reentrant interrupt processing within a supervisory environment.

MEMORY PROTECTION - Memory protection is a standard system feature which permits a program to be restricted within an area of memory as defined by two memory address limits. An attempt to write or execute outside of the restricted area results in a system trap interrupt. The limits defining a protected area of memory may be altered under program control. Memory protection on the System 2400 computer is primarily intended for use in a supervisory multiprogrammed environment where memory protection is dynamically activated for each task at the onset of its execution. REAL TIME CLOCK - The real time clock provides a low priority CPU interrupt each 16 2/3 milliseconds. The clock incorporates a watchdog timer which generates a system trap interrupt in case a clock interrupt is not acknowleged within 16 2/3 milliseconds.

POWER FAIL DETECTION - This feature insures orderly system shutdown and automatic restart in case of power failure.

PERIPHERALS - A complete line of peripheral equipment is \_\_\_\_\_ available for the System 2400 computer. Representative peripheral include:

Keyboard Printers - 10 characters per second. Also available with integrated paper-tape reader at 10 characters per second and punch at 10 characters per second.

Card Readers - .300, 600 and 1000 cards per minute. Read 80-column cards in parallel by column, photoelectrically. Automatic conversion to ASCII.

*Line Printers* - Fully buffered, 300, 600 and 1000 lines per minute, with 80 and 132 print positions.

Magnetic-Tape Units - Nine-track: IBM-compatible, 37.5 inches per second, 800 bytes per inch, 30,000 bytes per second transfer rate. Seven-track: IBM-compatible, 37.5 inches per second, 200, 556 and 800 bytes per inch, transfer rates of 7,500, 20,850 and 30,000 characters per second.

Disc Files - Capacity 831,488 to 8,304,880 words per storage unit; transfer rate of 104,000 words per second; average access times between 12.5 and 20 milliseconds.

Paper-Tape Readers and Punches - Readers with speeds of 10 and 500 characters per second. Punches with speeds of 10 and 120 characters per second. Both use eight-level codes.

Analog-To-Digital Converter - Analog-to-digital converters and multiplexers with sampling rates that exceed 40,000 samples per second for 12 bit resolution; low-level to high-level.

Digital-To-Analog Converters - 14-bit resolution, low impedance output, fast settling time, updating rates exceeding 100,000 channels per second.

Digital Inputs - 24-bit contact closure and voltage level inputs.

Digital Outputs - 24-bit contact closure and voltage level outputs.

*Process Inputs* - 24-bit contact closure and voltage level inputs that generate processor interrupts in response to external state or level variations.

SOFTWARE - A comprehensive package of systems oriented software is available for the 2400 computer. Representative software includes:

Multiprogramming Executive (MULTEX) - MULTEX is a disc oriented real time operating system designed to support priority oriented real time processing on the System 2400 computer. It provides for priority scheduling and functional support of multiple foreground tasks with concurrent background batch processing. Tasks may be permanently resident in memory or read from disc into memory for execution. A multiprogrammed mix of such tasks may be active at any given time with the highest priority task in actual execution.

MULTEX provides for automatic task scheduling based upon the system clock, the occurrence of an interrupt, or by task request. Interrupt scheduling may be performed in either direct or deferred mode. Direct interrupt scheduling is employed where critical response times are required and processing is performed at a priority level determined by hardware. Deferred interrupt scheduling is used where less critical response times are required and processing is performed at a priority level established by software.

MULTEX provides comprehensive input-output facilities at both the implicit and explicit levels which permit full I/O overlap with computing among separate tasks. Explicit I/O is inherently device dependent in nature as contrasted to implicit I/O which is device independent by definition. Implicit I/O is performed with respect to a system of file management which incorporates both disc files and I/O devices.

MULTEX provides for background batch processing at the lowest system priority level concurrent with foreground operation. The basic functions provided by the background system are indicated as follows:

- Assignment of Background I/O Units

- Assembly/Compilation

- On-line Creation of Foreground/Background Tasks

at in the

• Creation of Files

The list of background functions may be extended on-line to incorporate user written background tasks.

Assembler - The System 2400 assembler is available in both a stand-alone version and a version which operates as a MULTEX background task. The assembler provides the following basic features.

- User Defined Macro Procedures

- Conditional Assembly Capability

- Fixed and Floating Point Constants

- Absolute and/or Relocatable Object Code

Real Time Fortran - The System 2400 real time Fortran compiler operates as a MULTEX background task permitting foreground/background programs to be written in Fortran. The language exceeds USASI Basic Fortran standards and incorporates extensive file manipulation statements.

System Generation - The system generation program builds a version of MULTEX adapted to system configuration requirements. It operates as a stand-along program and accepts input from **a** master file of user specified system definition parameters.

Input-Output Drivers - Stand alone I/O drivers are provided for all system 2400 peripherals.

Diagnostic Programs - Stand-alone diagnostic programs are provided which permit comprehensive testing of selected System 2400 hardware components.

37 BC E4

B0 EC 20 ES

3A 3B

18

54

50 5C 9C 94 1C

# CODE (HEXADECIMAL) MNEMONIC INSTRUCTION

### CYCLES

ARITHMETIC

| ,    |     |      |      |      |      |       |   |

|------|-----|------|------|------|------|-------|---|

| Α    | Λ   | ١dd  |      |      |      |       |   |

| AD   | . Λ | \dd  | 1)οι | ib 1 | 0    |       |   |

| AIA  | Λ   | ١dd  | lnm  | od   | iate | A     |   |

| AIX  | Α   | \dd  | Imn  | ned  | iate | Х     |   |

| AIY  | Α   | ١dd  | Imn  | ned  | iate | Y     | * |

| AIZ  | Λ   | \dd  | Imn  | ned  | iate | Z     |   |

| DM   | Ľ   | )ecr | ceme | ent  | Mem  | ory   |   |

| D    | Ľ   | )ivi | de   |      |      |       |   |

| TM   | I   | [nci | ceme | ent  | Mem  | ory   |   |

| М    | N   | dult | :ip] | ly   |      |       |   |

| NEGA | N   | lega | ite  | Α    |      |       |   |

| NEGD | N   | Vega | nte  | Do   | uble |       |   |

| NEGX | N   | vega | nte  | Х    |      |       |   |

| NEGY | Ν   | Vega | ate  | Y    |      |       |   |

| NEGZ | N   | Vega | ate  | Ζ    |      |       |   |

| S    | S   | Subt | trad | ct   |      |       |   |

| SD   | 5   | Subt | trad | ct   | Doub | le    |   |

| SIA  | 5   | Subt | trad | ct   | Imme | diate | А |

| SIX  | 5   | Subt | trad | ct   | Imme | diate | Х |

| SIY  | 5   | Subt | trad | ct   | Imme | diate | Y |

| SIZ  | 5   | Subt | trad | ct   | Imme | diate | Z |

|      | 1   |      |      |      | /    |       |   |

#### BRANCH

| В   |      | Branch |                |

|-----|------|--------|----------------|

| BE  |      | Branch | if Equal       |

| BG  |      | Branch | if Greater     |

| BI  |      | Branch | Indirect       |

| BL  | 8.64 | Branch | if Less        |

| BNE |      | Branch | if Not Equal   |

| BNG |      | Branch | if Not Greater |

| BNL |      | Branch | if Not Less    |

| BNV |      | Branch | if No Overflow |

| BR  |      | Branch | and Restore    |

| BS  |      | Branch | and Save       |

| BV  |      | Branch | if Overflow    |

|     |      |        |                |

1 1

1 1

1

## INSTRUCTION SET

| (HEX                                                                                   | CODE<br>ADECIMAL) | MNEMONIC                                                                                               | INSTRUCTION                                                                                                                                                                                                                                                                                                                                                                                                                         | CYCLES                                                               |

|----------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                                                        | COMPARE           |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 70<br>FC<br>3D<br>3E<br>3F<br>74<br>78<br>7C                                           |                   | CPA<br>CPD<br>CIA<br>CIX<br>CIY<br>CIZ<br>CPX<br>CPY<br>CPZ                                            | Compare A<br>Compare Double<br>Compare Immediate A<br>Compare Immediate Y<br>Compare Immediate Z<br>Compare X<br>Compare Y<br>Compare Z                                                                                                                                                                                                                                                                                             | 2<br>3<br>1<br>1<br>1<br>1<br>2<br>2<br>2                            |

| •                                                                                      | LOGICAL           |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| A4<br>24<br>25<br>26<br>27<br>AC<br>2C<br>2D<br>2E<br>2F<br>A8<br>28<br>29<br>2A<br>2B |                   | N<br>NIA<br>NIX<br>NIY<br>NIZ<br>X<br>XIA<br>XIX<br>XIX<br>XIY<br>XIZ<br>O<br>OIA<br>OIX<br>OIY<br>OIZ | Logical And<br>Logical And Immediate A<br>Logical And Immediate X<br>Logical And Immediate Y<br>Logical And Immediate Z<br>Logical Exclusive Or<br>Logical Exclusive Or Immediate A<br>Logical Exclusive Or Immediate X<br>Logical Exclusive Or Immediate Y<br>Logical Exclusive Or Immediate Z<br>Logical Inclusive Or<br>Logical Inclusive Or Immediate A<br>Logical Inclusive Or Immediate A<br>Logical Inclusive Or Immediate X | 1<br>1<br>2<br>1<br>1<br>1                                           |

| C8<br>CC<br>C0<br>C4<br>D8<br>DC<br>D0<br>D0<br>D4                                     | SHIFT             | SLC<br>SLCD<br>SLL<br>SLLD<br>SRA<br>SRAD<br>SRL<br>SRLD                                               | Shift Left Closed<br>Shift Left Closed Double<br>Shift Left Logical<br>Shift Left Logical Double<br>Shift Right Algebraic<br>Shift Right Algebraic Double<br>Shift Right Logical<br>Shift Right Logical Double                                                                                                                                                                                                                      | 2+N/3<br>2+N/3<br>2+N/3<br>2+N/3<br>2+N/3<br>2+N/3<br>2+N/3<br>2+N/3 |

4 - 2

|    | CODE<br>(HEXADECIMAL) | MNEMONIC     | INSTRUCTION                     | CYCLES                                |

|----|-----------------------|--------------|---------------------------------|---------------------------------------|

|    | TRANSFER              | ·            |                                 |                                       |

|    |                       | ş.           |                                 |                                       |

|    | 05                    | CAX          | Сору А То Х                     | 1                                     |

|    | 06                    | CAY          | Сору Л То Ү                     | 1                                     |

|    | 07                    | CAZ          | Сору А То Ζ                     | 1                                     |

|    | 09 .                  | CXA          | Сору Х То А                     | 1                                     |

|    | 0.A                   | CYA          | Сору Ү То А                     | 1                                     |

|    | OB                    | CZA          | Copy Z To A                     | 1                                     |

|    | OD                    | IAX          | Interchange A and X             | 1                                     |

|    | 0E                    | IAY          | Interchange A and Y             | 1                                     |

|    | OF                    | IAZ          | Interchange A and Z             | 1                                     |

|    | 60                    | LDA          | Load A                          | 2                                     |

|    | FO                    | LDD          | Load Double                     | 3                                     |

|    | 30                    | LIA          | Load Immediate A                | 1.                                    |

|    | 31                    | LIX          | Load Immediate X                | 1                                     |

|    | 52                    | LIY          | Load Immediate Y                | 1                                     |

|    | 33                    | LIZ          | Load Immediate Z                | 1                                     |

|    | 64                    | LDX          | Load X                          | 2<br>2                                |

|    | 68                    | LDY          | Load Y                          | 2                                     |

|    | 6C                    | LDZ<br>. STA | Load Z                          | 2                                     |

|    | 40<br>E0              | STA          | Store A<br>Store D <b>ouble</b> | 2                                     |

|    | 44                    | STX          | Store X                         | 3<br>2<br>2                           |

|    | 48                    | STY          | Store Y                         | 2                                     |

|    | 40<br>4C              | STZ          | Store Z                         | 2                                     |

|    | 40                    | 012          |                                 |                                       |

|    | INPUT/OUTPU           | Т            |                                 |                                       |

|    | •                     |              | 6                               |                                       |

|    | 84                    | RD           | Read Direct 🕤                   | 2                                     |

|    | 80                    | RS           | Read Status                     | 2                                     |

|    | 8C                    | WD           | Write Direct                    | 2                                     |

|    | 88                    | WS           | Write Status                    | 2                                     |

|    |                       |              | •                               |                                       |

| 22 | MISCELLANEO           | 05           |                                 |                                       |

|    | 04                    | CV           | Clear Overflow                  | 1                                     |

|    | 02                    | DSI          | Disable Interrupts              | î 🖂                                   |

|    | 03                    | ENI          | Énable Interrupts               | ĩ                                     |

|    | Λ0                    | EX           | Execute                         | 1+INSTR                               |

|    | 00                    | HALT         | Halt                            | 1                                     |

|    | 01                    | NOP          | No Operation                    | 1                                     |

|    | 08                    | SV           | Set Overflow                    | 1                                     |

|    | 0C                    | SVC          | Supervisor Call                 | 1 , -                                 |

|    |                       |              |                                 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|    |                       |              |                                 |                                       |

#### INSTRUCTION FORMATS

Five instruction types are used in the dcs 2400 instruction set. All instructions occupy a single 24 bit word.

1. Memory Reference Instructions

The most commonly used instruction is the memory reference type instruction. These instructions can directly address the entire memory (0 to 32K words) with or without indexing. The A field in the instruction specifies a 16 bit signed displacement memory address. The X field specifies optional indexing with the contents of index registers Rx, Ry, or Rz. The effective memory address (actual memory address) is the sum of the A value with the contents of the specified index register.

| 0 5                                                                                                                            | 67                                                                                                      | 8                                                                                                                                                                                                                                                                                | 23  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| OP CODE                                                                                                                        | хх                                                                                                      | ± A .                                                                                                                                                                                                                                                                            |     |

|                                                                                                                                |                                                                                                         | ↑<br>16 bit, Direct Address                                                                                                                                                                                                                                                      |     |

|                                                                                                                                | 2 bi                                                                                                    | it, Index Tag                                                                                                                                                                                                                                                                    |     |

|                                                                                                                                |                                                                                                         | No Index<br>(Rx)<br>(Ry)<br>(Rz)                                                                                                                                                                                                                                                 |     |

| 6 bit, Open                                                                                                                    | atic                                                                                                    |                                                                                                                                                                                                                                                                                  | 1.1 |

| OP CODE                                                                                                                        | MNEM                                                                                                    | MONIC INSTRUCTION                                                                                                                                                                                                                                                                |     |

| 0001 10XX<br>1001 10XX<br>0001 00XX<br>0101 01XX<br>0101 10XX<br>0101 10XX<br>0101 11XX<br>1001 11XX<br>1001 01XX<br>0001 11XX | A<br>AD<br>B<br>BE<br>BG<br>BI<br>BL<br>BNE<br>BNE<br>BNC<br>BNL<br>BNV<br>BR<br>BS<br>BV<br>CPA<br>CPD | ADD<br>ADD DOUBLE<br>BRANCH<br>BRANCH IF EQUAL<br>BRANCH IF GREATER<br>BRANCH IF GREATER<br>BRANCH IF NOT EQUAL<br>BRANCH IF NOT GREATER<br>BRANCH IF NOT LESS<br>BRANCH IF NO OVERFLOW<br>BRANCH AND RESTORE<br>BRANCH AND SAVE<br>BRANCH IF OVERFLOW<br>COMPARE A<br>COMPARE A |     |

- A. . .

| OP CODE   | MNEMONIC | INSTRUCTION          |

|-----------|----------|----------------------|

| olli olxx | CPX      | COMPARE X            |

| 0111 10XX |          | COMPARE Y            |

| 0111 11XX |          | COMPARE Z            |

| 1011 11XX |          | DECREMENT MEMORY     |

| 1110 01XX |          | DIVIDE               |

| 1010 00XX | EX ·     | EXECUTE              |

| 1011 00XX | IM       | INCREMENT MEMORY     |

| 0110 00XX | LDA      | LOAD A               |

| 1111 00XX | LDD      | LOAD DOUBLE          |

| 0110 01XX | LDX      | LOAD X               |

| 0110 10XX | LDY      | LOAD Y               |

| 0110 11XX | LDZ      | LOAD Z               |

| 1010 01XX | N        | LOGICAL AND          |

| 1010 11XX | Х        | LOGICAL EXCLUSIVE OR |

| 1010 10XX | 0        | LOGICAL INCLUSIVE OR |

| 1110 11XX | М        | MULTIPLY             |

| 0100 00XX |          | STORE A              |

|           | STD      | STORE DOUBLE         |

| 0100 01XX |          | STORE X              |

| 0100 10XX |          | STORE Y              |

| 0100 11XX |          | STORE Z              |

| 1011 10XX |          | SUBTRACT             |

| 1111 10XX | SD       | SUBTRACT DOUBLE      |

#### 2. Immediate Instructions

The immediate instructions (also called Literal instructions) use the A field in the instruction word as the second operand. The first operand is contained in one of the working registers (Ra, Rx, Ry, or Rz) and the result if saved replaces the previous contents of the register. The least significant sixteen bits of the instruction becomes a 24 bit operand when the sign bit (bit 8) is extended into bits 0 to 7.

| 0                                                                                                                                                                                                                                                | 789                                                                                                                                                                                                     | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| OP CODE                                                                                                                                                                                                                                          | ±                                                                                                                                                                                                       | <u>م</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| S bit. Ope                                                                                                                                                                                                                                       | ↑<br>16 bit<br>eration Cod                                                                                                                                                                              | , Sign Extending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| OP CODE                                                                                                                                                                                                                                          | MNEMONIC                                                                                                                                                                                                | INSTRUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| 001101000011010100110110001101110011110100111101001111110011001000110010001100100010010100100101001001010010010100101101001011010010100100101011001010110010101100101011001110010011100100111011001110110011101100111011001110110011101100111011 | AIA<br>AIX<br>AIY<br>AIZ<br>CIA<br>CIX<br>CIY<br>CIZ<br>LIA<br>LIX<br>LIY<br>LIZ<br>NIA<br>NIX<br>NIY<br>NIZ<br>XIA<br>XIX<br>XIY<br>XIZ<br>OIA<br>OIX<br>OIX<br>OIX<br>OIX<br>SIA<br>SIX<br>SIY<br>SIZ | ADD IMMEDIATE A<br>ADD IMMEDIATE X<br>ADD IMMEDIATE Y<br>ADD IMMEDIATE Z<br>COMPARE IMMEDIATE A<br>COMPARE IMMEDIATE X<br>COMPARE IMMEDIATE Y<br>COMPARE IMMEDIATE Z<br>LOAD IMMEDIATE A<br>LOAD IMMEDIATE X<br>LOAD IMMEDIATE Y<br>LOAD IMMEDIATE Z<br>LOGICAL AND IMMEDIATE A<br>LOGICAL AND IMMEDIATE Y<br>LOGICAL AND IMMEDIATE Y<br>LOGICAL AND IMMEDIATE Z<br>LOGICAL AND IMMEDIATE Z<br>LOGICAL EXCLUSIVE OR IMMEDIATE<br>LOGICAL EXCLUSIVE OR IMMEDIATE<br>LOGICAL EXCLUSIVE OR IMMEDIATE<br>LOGICAL INCLUSIVE OR IMMEDIATE<br>SUBTRACT IMMEDIATE X<br>SUBTRACT IMMEDIATE X<br>SUBTRACT IMMEDIATE X<br>SUBTRACT IMMEDIATE X | X<br>Y<br>Z<br>A<br>X<br>Y |

#### 5. Shift Instruction

The shift instructions provide for arithmetic and logical manipulation of information contained in the Ra and Rd registers. The operation code specifies the register to be shifted and the type of shift operation to be performed. The number of bit positions to be shifted (N) is specified by the sum of the value A with the contents of the index register specified by X. After the shift count is modified by the index value, only the eight least significant bits are used. The shift count will be in the range 0 < N < 255.

| 0 5                   | 6789 23                                      |

|-----------------------|----------------------------------------------|

| OP CODE               | X X ± A                                      |

| Â                     | 16 bit, Sign Extending<br>2 bit, Index Tag   |

|                       | 00 No Index<br>01 (Rx)<br>10 (Ry)<br>11 (Rz) |

| 6 hit One             | ration Code                                  |

| 6 bit, Ope<br>OP CODE | NNEMONIC INSTRUCTION                         |

13

ş

Register-Register and Control Instructions

4.

The register-register and control instructions use only the operation code field. Bits 8-23 in the instruction are ignored. The register-register instructions move information between the working registers. The control instructions control the CPU and interrupt system status.

| _ | 0                            | 78        |      |         |        |        |     | 23 |

|---|------------------------------|-----------|------|---------|--------|--------|-----|----|

|   | OP COI                       | DE        |      |         |        |        |     |    |

| • | ↑<br>8 bit, (                | Operation | Code | 9       |        |        |     |    |

|   | OP CODE                      | MNEMON    | IC   | INSTRUC | TION   |        |     |    |

|   | 0000 010                     | 01 CAX    |      | COPY A  | то х   |        |     |    |

|   | 0000 01                      | 10 CAY    |      | COPY A  | ΤΟ Υ   |        |     |    |

|   | 0000 01                      | 11 CAZ    |      | COPY A  | TO Z   |        |     |    |

|   | 0000 100                     | 01 CXA    |      | СОРУ Х  | TO A   |        |     |    |

|   | 0000 10                      | 10 CYA    |      | COPY Y  | TO A   |        |     |    |

|   | 0000 10                      | ll CZA    |      | COPY Z  | TO A   |        |     |    |

|   | 0000 100                     | 00 CV     |      | CLEAR C | VERFI  | LOW    |     |    |

|   | 0000 001                     | 10 DSI    |      | DISABLE | E INTE | ERRUPI | ſS  |    |

|   | 0000 001                     | 11 ENI    |      | ENABLE  | INTEF  | RUPTS  | 5   |    |

|   | 0000 000                     | 00 HALT   |      | HALT    |        |        |     |    |

|   | 0000 110                     | Ol IAX    |      | INTERCH | IANGE  | A ANI  | Х   |    |

|   | 0000 11                      | 10 IAY    |      | INTERCH | IANGE  | A ANI  | Υ   |    |

|   | 0000 11                      | 11 IAZ    |      | INTERCH | IANGE  | A ANI  | ) Z |    |

| , | 0010 000                     | 00 y NEGA |      | NEGATE  | А      |        |     | 3  |

|   | 1110 100                     | 00 NEGD   |      | NEGATE  | DOUBI  | E      |     |    |

|   |                              | 01 NEGX   |      | NEGATE  | Х      |        |     |    |

|   |                              | 10 NEGY   |      | NEGATE  |        |        |     |    |

|   |                              | 11 NEGZ   |      | NEGATE  |        |        |     |    |

|   | 0000 000                     |           |      | NO OPER |        |        |     |    |

| ; | 0000_010                     | 00 SV     |      | SET OVE | RFLOW  | I      |     |    |

|   | <ul> <li>C. 1 (2)</li> </ul> |           |      |         |        |        |     |    |

## 5. Input-Output Instructions

The input-output instructions transfer data, status and control information directly between the Ra register and the input-output system. Input-output device addresses are computed in the same way effective memory addresses are computed for memory reference instructions. The device address is the sum of the value A with the contents of the specified index register.

| 0 5        | 6 7 8                |                                                            | 23 |

|------------|----------------------|------------------------------------------------------------|----|

| OP CODE    | X X ±                | A                                                          | -  |

|            |                      | bit, Device Address<br>Index Tag                           |    |

|            |                      | Index<br>()<br>()                                          |    |

| 6 bit, Ope | ration C             | Code                                                       |    |

| OP CODE    | MNEMONI              | C INSTRUCTION                                              |    |

| 1000 00XX  | RD<br>RS<br>WS<br>WD | READ DIRECT<br>READ STATUS<br>WRITE STATUS<br>WRITE DIRECT |    |

#### DATA FORMATS

Three types of formats are used to represent numerical data: (1) Integer, (2) Double Precision, (3) Floating Point.

1. Integer

The basic data format is a 24 bit signed 2's complement binary integer.

| 0 1 | -    | 23 |

|-----|------|----|

| S   | DATA |    |

| L   |      |    |

Sign Bit 0 = Positive 1 = Negative

The number represented is defined as a binary or hexadecimal integer, with bit 0 being the most significant position, and bit 23 the least significant.

The maximum range of signed integers which may be represented by a single word is  $80000016 \le 1 \le 7FFFF16$ (decimal:- $8388608 \le 1 \le +8388607$ ). Negative quantities are expressed in 2's complement form. (The 2's complement of a number is obtained by inverting each bit of the binary number and adding one.)

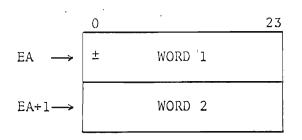

#### 2. Double Precision

Double Precision arithmetic utilizes two machine words to represent a 48 bit, signed binary integer with the following format:

| 0 1 |        | 2324 |                                                                                                                 | 47 |

|-----|--------|------|-----------------------------------------------------------------------------------------------------------------|----|

| S   | WORD 1 | DATA | WORD 2                                                                                                          |    |

|     |        |      | Contraction of the second s |    |

Sign Bit 0 = Positive 1 = Negative Numbers up to  $2^{47}$  may be represented in this format. The minimum range is  $8000000000_{16} \le 1 \le 7FFFFFFFFFFFf6$ (decimal:-140737488344328 $\le 1 \le 14073788355237$ ). Negative double precision numbers are represented in 2's complement form.

The effective memory address of a double precision operand specifies the address of the most significant half of the operand. The least significant half is located at the effective memory address plus one.

(LEAST SIGNIFICANT)

(MOST SIGNIFICANT)

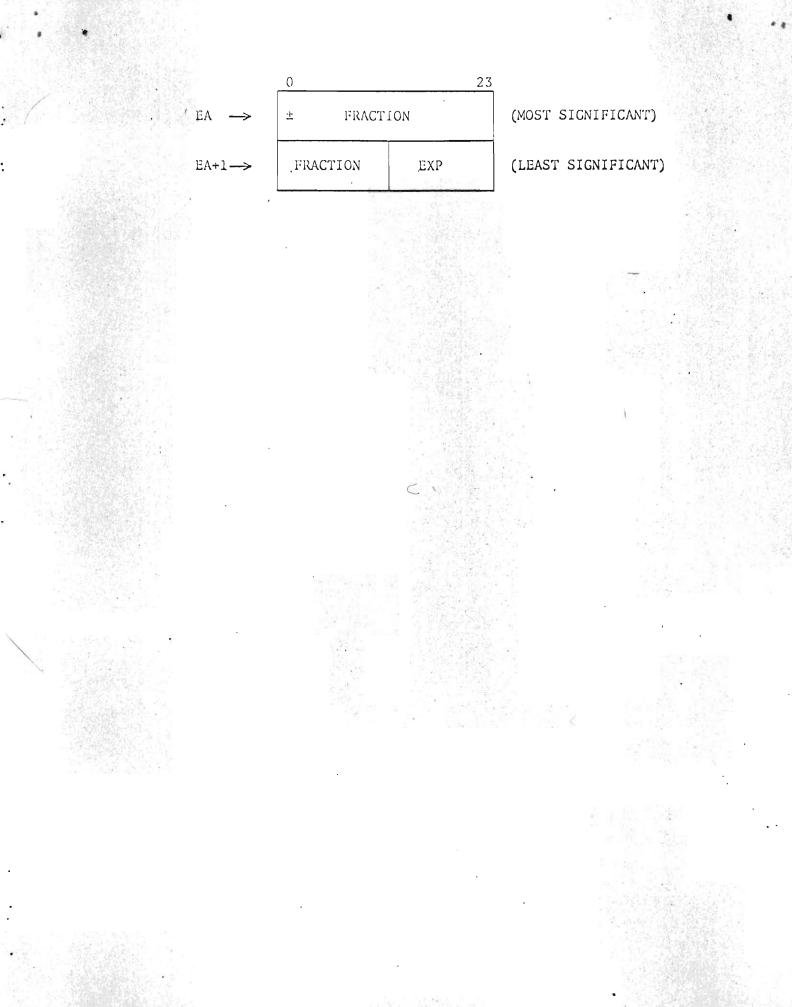

#### 3. Floating Point

The floating point format used two machine words to represent the floating point number.

| 0 1 | 2324     | 3940     | 47  |

|-----|----------|----------|-----|

| S   | FRACTION | EXP+128, | . 0 |

Sign Bit

| 40 | Bit | Signed | Fraction | 8 Bit    |

|----|-----|--------|----------|----------|

|    |     |        |          | Exponent |

The 40 bit signed 2's complement fraction occupies bits 0-39 and the 8 bit excess 128 exponent occupies bit 40-47. The radix point of the fraction is assumed to be immediately to the left of the high order fraction digit.

The effective memory address of a floating point operand specifies the address of the most significant half of the fraction. The least significant half of the fraction and the exponent are located at the effective memory address plus one.

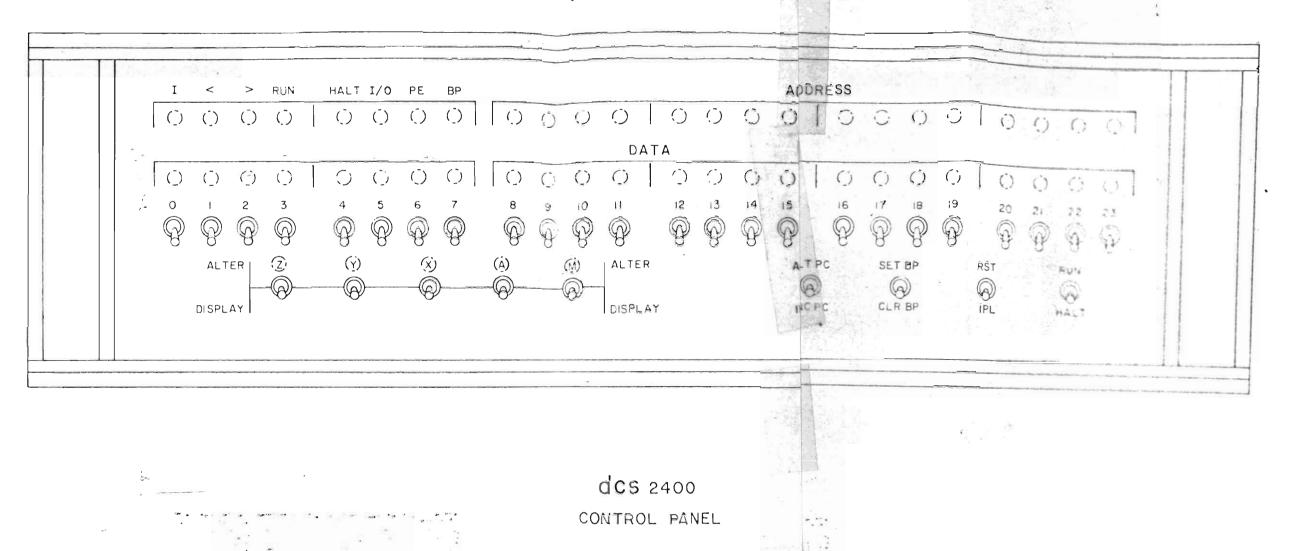

#### CONTROL PANEL

Controls and Indicators

Address Display - 16 bit indicator that displays and CPU address buss. When the CPU is in the halt mode this indicator displays the contents of the program counter.

Data Display - 24 bit indicator that displays the CPU data buss. When the CPU is in the halt mode this indicator displays the contents of the register or memory location selected by the display control switches.

Status Display - 8 bit indicator displays the program status.

- I If lighted this display indicates that the interrupt system is ENABLED.

- < If lighted this display indicates that the algebraic result of the last arithmetic or logical operation was LESS THAN ZERO.

- If lighted this display indicates that the algebraic result of the last arithmetic or logical operation was GREATER THAN ZERO.

If both the < and > indicators are lighted, the last arithmetic or shift operation resulted in an ARITHMETIC OVERFLOW.

- RUN If lighted this display indicates that the CPU is in the RUN mode.

- HALT If lighted this display indicates that the CPU is in the HALT mode.

- I/O If lighted this display indicates that an input or output operation is in progress.

- PE If lighted this display indicates that a memory PARITY ERROR has occurred. The occurrence of a parity error will halt the CPU.

- BP If lighted this display indicates that a program BREAKPOINT is set.

Data Switch Register - 24 bit switch register used to enter address and data information.

0.0

5-1

Run - This momentary contact switch places the CPU in the run mode. Instruction execution starts at the memory address stored in the program counter.

Halt - This momentary contact switch places the CPU in the halt mode. Instruction execution stops with the address of the next instruction to be executed stored in the program counter. If the CPU is in the halt mode, operation of the halt switch will cause a single instruction to be executed each time the switch is operated.

Reset - This momentary contact switch resets the CPU and all input-output control units. This switch is operational only when the CPU is halted.

IPL - This momentary contact switch initiates an initial program load operation from a preselected input-output device. This switch is operational only when the CPU is halted.

Alter PC - This momentary contact switch causes the address set in bits 8-23 of the data switch register to be copied into the program counter and displayed in the address display. The contents of the memory location addressed by the program counter will be displayed in the data display.

Increment PC - This momentary contact switch causes one to be added to the contents of the program counter. The new contents of the program counter will be displayed in the address display. The contents of the memory location addressed by the program counter will be displayed in the data display.

Alter MEM - This momentary contact switch causes the data word set in the data switch register to be copied into the memory location addressed by the program counter. The new contents of the memory location will be displayed in the data display.

Display MEM - This momentary contact switch causes the contents of the memory location addressed by the program counter to be displayed in the data display.

Alter Ra - This momentary contact switch causes the data word set in the data switch register to be copied into the Ra register. The new contents of the Ra register will be displayed in the data display.

Display Ra - This momentary contact switch causes the contents of the Ra register to be displayed in the data display. Alter Rx - This momentary contact switch causes the data word set in the data switch register to be copied into the Rx register. The new contents of the Rx register will be displayed in the data display.

Display Rx - This momentary contact switch causes the contents of the Rx register to be displayed in the data display.

Alter Ry - This momentary contact switch causes the data word set in the data switch register to be copied into the Ry register. The new contents of the Ry register will be displayed in the data display.

Display Ry - This momentary contact switch causes the contents of the Ry register to be displayed in the data display.

Alter Rz - This momentary contact switch causes the data word set in the data switch register to be copied into the Rz register. The new contents of the Rz register will be displayed in the data display.

Display Rz - This momentary contact switch causes the contents of the Rz register to be displayed in the data display.

#### ASSEMBLY LANGUAGE

#### GENERAL

The System 2400 Assembly Language is a symbolic programming language which facilitates the construction of machine language programs through the use of symbolic notation for machine instructions and data. The translation of an assembly language program into its machine language representation is performed by an assembler program. The assembly process is one of converting information expressed in assembly language into equivalent information expressed in machine language.

The fundamental program element is the statement. A program represented as a sequence of statements recorded on an external medium is referred to as a source program. The assembler reads and translates the source program into an equivalent machine language object program. The translation procedure requires two separate passes or readings of the source program. During pass one a table of program symbols is built for reference during pass two. Pass two provides a printed listing of the assembled program and an external record of the resulting object program which may be loaded into the computer for execution.

#### STATEMENTS

Statements are of three basic types: Comment, Instruction, and Directive.

Comment statements serve as program documentation aids and are simply reproduced on the program listing. A comment statement is indicated by an asterisk (\*) in statement position one.

Instruction statements are translated directly by the assembler into corresponding machine instructions.

Directive statements are special instructions to the assembler which serve to direct the assembly process and generate various forms of data.

Instruction and Directive statements are subdivided into three fixed length statement fields:

Statement Position:

1-6 Label Field8-13 Operation Field15-72 Operand Field

Following the first blank operand position, the remainder of the statement is ignored and is available for comments.

Label Field

The Label Field optionally contains a statement label consisting of from one to six alphanumeric characters with the first character alphabetic.

Operation Field

The Operation Field contains an operation mnemonic associated with an instruction or assembler directive.

Operand Field

The Operand Field contains one or more operands associated with the operation to be performed.

#### LOCATION COUNTER

The Location Counter is used by the assembler to assign consecutive addresses to statement derived object code. The location counter is absolute if it represents an actual memory address and relocatable if it represents a relative displacement from the beginning of the program. In the relocatable case, the initial value of the location counter is specified at load time as a relocation bias corresponding to the address in memory at which the program is to originate. The location counter is initialized by the assembler to relocatable zero and is controlled by the ORG assembler directive.

#### TERMS

Terms are the basic units required in building expressions. A term may be absolute or relocatable depending upon its type and the mode of the location counter at the time it is defined.

#### Asterisk

The Asterisk (\*) is a term representing the current value and mode of the location counter.

#### Symbol

A Symbol consists of from one to six alphanumeric characters with the first character alphabetic. A symbol is usually defined by its appearance as a statement label and is assigned the value and mode of the location counter at the time it is encountered.

#### Constant

Constant terms are absolute and are assigned their indicated values. There are three types of constant terms: Hexadecimal, Decimal, and Character.

Hexadecimal Constant

A Hexadecimal Constant consists of a single hexadecimal number, consisting of at most six hexadecimal digits, enclosed in apostrophes and preceded by the letter X.

| Examples: | X.'3AF'  |

|-----------|----------|

| -         | X'1000'  |

|           | X'FFFFF0 |

Decimal Constant

A Decimal Constant consists of from one to seven decimal digits in the numeric range 0 to 8,388,607.

> Examples: 100 10000 6999500

#### Character Constant

A Character Constant consists of a single ASCII character enclosed in apostrophes and preceded by the letter C.

| Examples: | C'A' |

|-----------|------|

| -         | C'+' |

|           | CIII |

#### EXPRESSIONS

Expressions are formed by combining terms from left to right using the following arithmetic operators:

- + Addition

- Subtraction

- \* Multiplication

- / Division

The first term of an expression may be preceded by a minus sign to indicate negation. An expression is absolute if the net number of relocatable terms is zero and relocatable if the net number of relocatable terms is one. Each operand address generated by a relocatable expression must be modified at load time by adding the relocation bias in order to obtain a corresponding memory address. This function is performed by the loader in addition to program storage allocation.

#### DIRECTIVES

Directives are special instructions to the assembler relating to assembly control and data generation. Each directive is identified by a symbolic operation mnemonic which is written in the operation field of the statement. With the exception of the EQU directive, a label appearing within the label field of an assembler directive is assigned the value and mode of the location counter prior to processing the directive.

Define Orign (ORG)

The location counter is set to the value and mode of the expression appearing in the operand field.

| Examples: | ORG | 0       |

|-----------|-----|---------|

| -         | ORG | X'1000' |

|           | ORG | *+16    |

|           | ORG | BEGIN+6 |

|           |     |         |

Define Equivalence (EQU)

The label appearing in the label field is assigned the value and mode of the expression appearing in the operand field.

| Examples: | TEN   | EQU | 10      |

|-----------|-------|-----|---------|

|           | TEMP2 | EQU | TEMP+2  |

|           | CON6  | EQU | X'4AFO' |

Define Constant (DC)

The constants appearing in the operand field are evaluated and generated into consecutive storage words. Each line of constant data is identified by a single character type mnemonic followed by one or more constant items separated by commas and enclosed in apostrophes. The type mnemonic may be preceded by an optional integer repeat constant which specifies the number of line copies to be generated.

Hexadecimal, Type X

An X type constant consists of the letter X followed by one or more hexadecimal numbers separated by commas and enclosed in apostrophes. One storage word is generated for each constant item.

| Examples: | DC | X'400000'       |

|-----------|----|-----------------|

| -         | DC | X'16FC,12AB6'   |

|           | DC | 4X'20'          |

|           | DC | 10X'0,0,FFFFFF' |

Single Word, Type S

A type S constant consists of the letter S followed by one or more expressions separated by commas and enclosed in apostrophes. One storage word is generated for each item specified.

| Examples: | DC | S'-4'            |

|-----------|----|------------------|

| •         | DC | S'TEMP+2'        |

|           | DC | 10S'0'           |

|           | DC | S'1,10,100,1000' |

Double Word, Type D

A type D constant consists of the letter D followed by one or more double word constants separated by commas and enclosed in apostrophes. Two types of double word constants are permitted:

> Fixed Point: ±M Floating Point: ±M.N±E

M, N, and E are strings of decimal digits representing the integer, fraction, and exponent parts of the constant, respectively, and may be omitted when zero. Fixed point constants are distinguished from floating point constants by the absence of both a decimal point and exponent. The repeat constant, if specified, is interpreted as a signed fixed point binary scale factor. In this case, the constant is converted to its fixed point representation at the specified scale. Two storage words are generated for each constant item.

| Examples: | DC | D'.125'       |

|-----------|----|---------------|

| -         | DC | D'2554-3'     |

|           | DC | D'125000'     |

|           | DC | 23D'45.99656' |

ASCII, Type A

A type A constant consists of the letter A followed by a string of characters enclosed in apostrophes. The characters are generated into consecutive storage words and packed three characters per word beginning with the left byte of the first word. Additionally, a one or two digit hexadecimal number enclosed in abostrophes appearing within the string is evaluated and generated into the next available character position.

| Examples: | DC | A'CHARACTER STRING |

|-----------|----|--------------------|

| •         | DC | A'MESSAGE'OD''OA'' |

|           | DC | 2041               |

Character, Type C. g.

A type C constant consists of the letter C followed by a string of characters enclosed in apostrophes. The characters are generated into consecutive storage words with one storage word allocated for each character.

|   | Examples: | DC | C'A'     |

|---|-----------|----|----------|

| 4 | -         | DC | C'ABCDE' |

|   |           | DC | 4C' '    |

Define Storage (DS)

The number of words indicated by the value of the absolute operand expression are reserved in storage.

| Examples: | DS | 10    |

|-----------|----|-------|

|           | DS | X'64' |

| ¥<br>2    | DS | 0     |

Define Entry Symbols (ENTRY)

The symbols appearing in the operand field correspond to statement labels which may be referenced by other programs to permit symbolic interprogram linkage.

| Examples: | ENTRY | FADD,FSUB |

|-----------|-------|-----------|

|           | ENTRY | SQRT      |

Define External Symbols (EXTRN)

The symbols appearing in the operand field correspond to entry symbols in one or more external programs which are to be loaded following the current program. An external symbol may appear only as an isolated term within the operand of a memory reference instruction or type S DC directive. Evaluation of address operands generated by external symbols is performed by the loader at load time.

> Examples: EXTRN FMUL, FDIV EXTRN SIN

#### Conditional Assembly (IFZ, IFP, IFN, IFNZ, IFNP, IFNN)

The first operand expression is evaluated and tested against the selected IF condition. If the condition is true, the number of successive statements indicated by the value of the absolute second operand expression are ignored by the assembler. If a second operand is not specified, all successive statements are ignored until an END or ENDIF directive is encountered. The permissable IF conditions are indicated as follows:

> IFZ - IF Zero (=0) IFP - IF Positive (>0) IFN - IF Negative (<0) IFNZ - IF Not Zero ( $\frac{1}{7}$ 0) IFNP - IF Not Positive (<0) IFNN - IF Not Negative ( $\geq$ 0) Examples: IFZ COND IFNP OPTION-1.4

End Conditional Assembly (ENDIF)

Assembly unconditionally proceeds with the next source statement.

Define Macro (MACRO)

A macro procedure is defined and assigned the name appearing in the label field. The first absolute operand expression specifies the number M of statements comprising the macro and the second absolute operand expression specifies the number N of macro parameters. The macro statement is followed by M statements which comprise the macro skeleton. Each statement may specify dummy macro parameters which are to be replaced by specific arguments when the macro is referenced. Each dummy parameter consists of the '#' character followed by an integer i in the range 0<i<N. A macro is referenced by writing the macro name in the operation field and a list of arguments separated by commas in the operand field which are to be substituted for the dummy parameters in the order: first argument-#0, second argument-#1, etc. The single parameter '#' represents the number of arguments present in the last macro reference and may be used in conjunction with conditional assembly directives th facilitate the construction of variable argument macros. A macro definition may incorporate any number of macro references; however, a macro must be defined prior to being referenced.

Example 1:

2

Storage to Storage MOVE Macro.

Macro Definition:

MOVE MACRO 2,2 LDA #0 STA #1

Macro Reference:

MOVE TEMP, ARG+4

Generated Statements:

LDA TEMP STA ARG+4

#### Example 2: Variable Argument CALL Macro.

Macro Definition:

CALL MACRO 5,3 BS #0 IFN #-2,3 DC S'#1' IFN #-3,1 DC S'#2'

Macro Reference:

CALL SUB

Generated Statements:

BS SUB

Macro Reference:

CALL SUB, ARG1, ARG2

Generated Statements:

| BS | SUB     |

|----|---------|

| DC | S'ARG1' |

| DC | S'ARG2' |

Program End (END)

The END statement indicates the end of the source program. The operand expression specifies the execution entry address of the program.

Listing Control Directives

The following assembler directives control the format of the program listing and are not printed on the list.

Program Title (TITLE)

The character string appearing in the operand field is printed at the top of each page of the listing.

New Page (PAGE)

The print device is advanced to a new page prior to printing the next statement.

Space Listing (SPACE)

The listing is spaced forward the number of lines indicated by the value of the absolute operand expression.

Suppress Listing (NOLIST)

Listing of statements following the NOLIST directive is suppressed.

Resume Listing (LIST)

Listing of statements following the LIST directive is resumed.

Suppress Generated Data Listing (NODATA)

Listing of constant data generated by DC directives is suppressed.

Resume Generated Data Listing (DATA)

Listing of DC generated constant data is resumed.

Suppress Macro Statement Listing (NOSTAT)

Listing of symbolic macro statements is suppressed.

Suppress Conditional Statement Listing (NOCOND)

Listing of conditional assembly statements and all statements which are not assembled is suppressed.

#### INSTRUCTIONS

Instruction statements are translated by the assembler into corresponding machine instructions. Each instruction statement is identified by a symbolic instruction mnemonic which is written in the operation field of the statement. A label appearing in the label field of an instruction statement is assigned the current value and mode of the location counter.

#### Class I, Memory Reference

| А   | Add .                 |

|-----|-----------------------|

| AD  | Add Double            |

| В   | Branch                |

| BE  | Branch if Equal       |

| BG  | Branch if Greater     |

| BI  | Branch Indirect       |

| BL  | Branch if Less        |

| BNE | Branch if Not Equal   |

| BNG | Branch if Not Greater |

| BNL | Branch if Not Less    |

| BNV | Branch if No Overflow |

| BR  | Branch and Restore    |

| BS  | Branch and Save       |

| ΒV  | Branch if Overflow    |

| CPA | Compare A             |

| CPD | Compare Double        |

| СРХ | Compare X             |

| CPY | Compare Y             |

| CPZ | Compare Z             |

| D   | Divide                |

| DM  | Decrement Memory     |

|-----|----------------------|

| EX  | Execute              |

| IM  | Increment Memory     |

| LDA | Load A               |

| LDD | Load Double          |

| LDX | Load X               |

| LDY | Load Y               |

| LDZ | Load Z               |

| М   | Multiply             |

| N   | Logical AND          |

| 0   | Logical Inclusive OR |

| S   | Subtract             |

| SD  | Subtract Double      |

| STA | Store A              |

| STD | Store Double         |

| STX | Store X              |

| STY | Store Y              |

| STZ | Store Z              |

|     | Logical Exclusive OR |

Operands:

A Direct, No IndexingA,X Indexed using RxA,Y Indexed using RyA,Z Indexed using Rz

A: An absolute or relocatable expression in the numerical range - 32768<A<32767 which specifies a memory or displacement address.

| Class             | II, Immediate                                              |        |

|-------------------|------------------------------------------------------------|--------|

| AIA<br>AIX        | Add Immediate A<br>Add Immediate X                         |        |

| ATY<br>ATZ<br>CIA | Add Immediate Y<br>Add Immediate Z<br>Compare Immediate    | Λ      |

| CIX<br>CIY        | Compare Immediate<br>Compare Immediate                     | X<br>Y |

| CIZ<br>LIA<br>LIX | Compare Inunediate<br>Load Immediate A<br>Load Immediate X | Z      |

| LIY<br>LIZ        | Load Immediate Y<br>Load Immediate Z                       |        |

| NIA<br>NIX        | AND Immediate A<br>AND Immediate X                         |        |

:

| NIY   | AND Immediate Y          |  |

|-------|--------------------------|--|

| NIZ : | AND Immediate Z          |  |

| AIO   | Inclusive OR Immediate A |  |

| OIX   | Inclusive OR Immediate X |  |

| YIO   | Inclusive OR Immediate Y |  |

| OIZ   | Inclusive OR Immediate Z |  |

| SIA   | Subtract Immediate A     |  |

| SIX   | Subtract Immediate X     |  |

| SIY   | Subtract Immediate Y     |  |

| SIZ   | Subtract Immediate Z     |  |

| XIA   | Exclusive OR Immediate A |  |

| XIX   | Exclusive OR Immediate X |  |

| XIY   | Exclusive OR Immediate Y |  |

| XIZ   | Exclusive OR Immediate Z |  |

Operands: A

A: An absolute or relocatable expression in the numerical range -32768<A<32767 which specifies an immediate operand.

Class III, Shift

| SLC  | Shift Left Closed         | SRA Shift Right Algebraic         |

|------|---------------------------|-----------------------------------|

| SLCD | Shift Left Closed Double  | SRAD Shift Right Algebraic Double |

| SLL  | Shift Left Logical        | SRL Shift Right Logical           |

| SLLD | Shift Left Logical Double | SRLD Shift Right Logical Double   |

Operands:

| A * | Direct  |       |               |  |

|-----|---------|-------|---------------|--|

|     | Indexed | using | $R\mathbf{x}$ |  |

| A,Y | Indexed | using | Ry            |  |

| A,Z | Indexed | using | Rz            |  |

|     |         |       |               |  |

A: An absolute expression in the numerical range -32768<A<32767 which specifies a shift or displacement count. Class IV, Input-Output

| RD | Read Direct | WD Write I | Direct |

|----|-------------|------------|--------|

| RS | Read Status | WS Write S | Status |

Operands:

•

A Direct

A,X Indexed using Rx

A,Y Indexed using Ry

A,Z Indexed using Rz

A: An absolute expression in the numerical range -32768<A<32767 which specifies a device or displacement address.

#### Class V, Register-Register and Control

| САХ  | Copy A to X        |

|------|--------------------|

| CAY  | Copy A to Y        |

| CAZ  | Copy A to Z        |

| CXA  | Copy X and A       |

| CYA  | Copy Y and A       |

| CZA  | Copy Z and A       |

| CV   | Clear Overflow     |

| DSI  | Disable Interrupts |

| ENI  | Enable Interrupts  |

| HALT | Halt               |

IAX Interchange A and X IAY Interchange A and Y IAZ Interchange A and Z NEGA Negate A NEGD Negate Double NEGX Negate X NEGY Negate Y NEGZ Negate Z NOP No Operation Set Overflow SV

Operands: None

Class VI, Supervisor Call

SVC Supervisor Call

Cperands: A

A: An absolute expression in the numerical range -32768<A<32767 which specifies a supervisor call index.

#### ASSEMBLY ERRORS

Errors detected during assembly are indicated on the program lsiting by a single error flag. The error flags and their meanings are indicated as follows:

- Pass Error. A statement label has a calculated pass two value different from the value assigned during pass one. This condition may result from data loss during one of the source passes or as the result of a symbol not being defined prior to its reference within the operand of an ORG or DS assembler directive.

- Undefined Op Code. The operand field does not contain a recognized instruction or directive mnemonic.

- L Label Field Error. The contents of the label field violate label syntax requirements.

- D Doubly Defined Label. The label appearing in the label field has appeared elsewhere as a statement label. The value assigned at the first occurance is used.

- S Statement Error. The contents of the operand field violate statement syntax requirements.

- U Undefined Symbol. A symbol appearing in the operand field has not been defined in any program statement.

C - Constant Error. An operand constant has been incorrectly specified or does not lie in the correct numerical range.

E - Expression Error. An expression appearing in the operand field has an improper mode or does not lie in the correct numerical range.

#### PROGRAM LISTING

The program listing is printed during pass two with listing fields for error flag, location counter, instruction, and statement number in the indicated print positions:

- Error Flag

5-6 Location Counter (Hexadecimal)

8-13 Instruction (Hexadecimal)

15-18 Statement Number (Decimal)

20- Source Statement

1

The listing is printed with 56 lines per page. Each page is \_\_numbered in decimal.