| OPERATOR'S & MAINTENANCE MANUAL     |               |

|-------------------------------------|---------------|

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

| LGP-20                              |               |

|                                     |               |

| Operators and Maintenance<br>Manual |               |

| Comdyna, Inc.                       |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     |               |

|                                     | COMDYNA, Inc. |

## LGP-20

## Operators & Maintenance Manual

## TABLE OF CONTENTS

| SECTION                                                                   | 1.                                                                                                      | LGP-20                                                                                                | OPERATING                                                                                                | PROCEDU                                                   | RES                              |                     |       |      |     |      | page                                                        |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------|---------------------|-------|------|-----|------|-------------------------------------------------------------|

| 1.0<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.A | Cali<br>Sett<br>Sett<br>Digi<br>Setti<br>Measu<br>Mode<br>Prob<br>Slav<br>Over:                         | bratic<br>ing Coe<br>ing th<br>tal Volting Ini<br>arement<br>Contro<br>lem Sol<br>ing Two<br>range of | of Externation of Reado fficient Pe Compute Temeter Meastial Conditof the Sumlution or More Unf Amplifie | ut Instotention ime Per urement tions of Int nits er Outp | rument neters iod as of A egrato | s<br>mplif<br>r Inp | ier O | utpı | ıts | •    | 1 2 2 2 2 2 3 3 3 4 5 5 5 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6   |

| SECTION                                                                   | 2.                                                                                                      | LGP-20                                                                                                | OPERATOR F                                                                                               | UNCTION                                                   | S                                |                     |       |      |     |      |                                                             |

| 2.0<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                      | Y/Po-<br>X Add<br>Mode<br>Comp<br>Digi<br>Over:                                                         | t Addre<br>dress<br>Contro<br>ute Tim<br>tal Vol<br>range A                                           | r Functionss                                                                                             |                                                           |                                  |                     |       |      |     |      | 6.<br>6.<br>7.<br>7.                                        |

| SECTION                                                                   | 3.                                                                                                      | PATCH F                                                                                               | 'ANELS                                                                                                   |                                                           |                                  |                     |       |      |     |      |                                                             |

| Patcl Si II At Mi Si D: T: S Micr Patcl Op Co NC                          | h Panummer: nvert ntegr ttenu ultip quare iffer rack/ ingle ohyb: h Pan perat; A Swi ompara AND GOR Gat | er                                                                                                    | ltage Divid<br>vider<br>e Root Ext<br>r.<br>Double Thr<br>atch Panel                                     | er.<br>ractor.<br>ow Elec<br>Layout                       | tronic                           | Swit                | ch    |      |     |      | 11.<br>11.<br>12.<br>13.<br>13.<br>14.<br>14.<br>14.<br>15. |

|                                                                           |                                                                                                         | _                                                                                                     | Counter<br>DIAGRAMS                                                                                      |                                                           |                                  |                     |       |      |     | <br> | <br>18.                                                     |

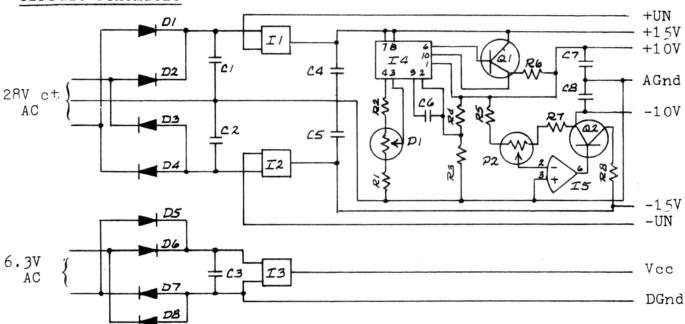

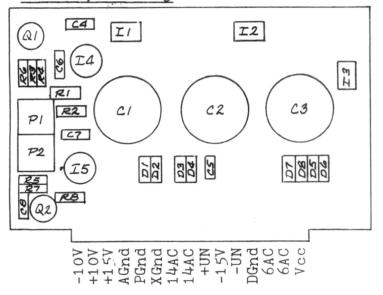

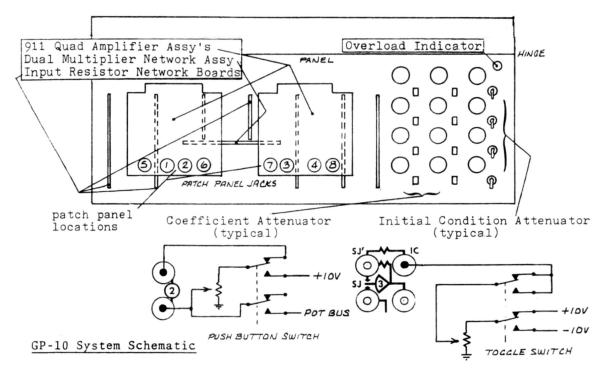

| Digi<br>Regui<br>GP-10<br>Qua<br>Ove<br>Dua<br>Micro                      | tal V lator Comp ad Am erload al Mu ohybr nel M                                                         | oltmeter, 7913. uting U plifier Indica ltipli id I punted C                                           | nit. Assembly, ator, 970. er Network,                                                                    | 911<br>982<br>pard Ass                                    | semblies                         |                     |       |      |     |      | <br>21.<br>23.<br>25.<br>27.<br>29.<br>31.                  |

## 1. OPERATING PROCEDURES

#### 1.0 CONNECTION OF EXTERNAL READOUT INSTRUMENTS

The LGP-20 offers a choice of slow and fast time scales. Slow time outputs are normally recorded with an XY plotter or strip chart recorder; fast time outputs are normally displayed by an oscilloscope.

A time base is provided and should be used wherever possible as the X input to an XY plotter or XY oscilloscope. Use of the internal time base offers two advantages.

1. The time base is calibrated to match the integrator time scales.

2. I t sweeps across a fixed range of coordinates regardless of the time period being plotter or displayed.

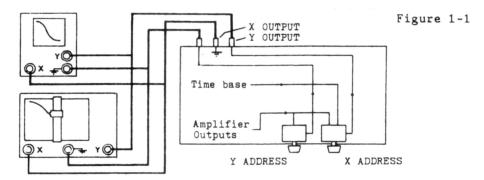

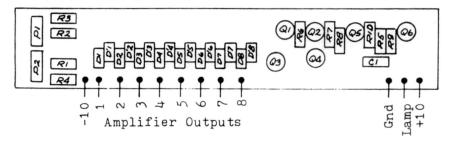

Rear binding post terminals offer convenient connections to the X and Y inputs of the plotter and/or oscilloscope. The three connections are shown in Figure 1-1 and listed below.

- 1. GND...signal ground.

- 2. Y OUTPUT...selection of the Y ADDRESS switch, to be connected as the plotter and/or oscilloscope vertical input.

- X OUTPUT...selection of the X ADDRESS switch, to be connected as the horizontal input.

#### 1.1 CALIBRATION OF READOUT INSTRUMENTS

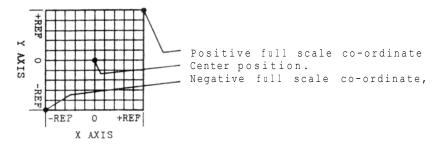

The range and zero position of a plotter or oscilloscope should be selected and positioned so that their full scale horizontal and vertical axes span the LGP-20 minus and plus ten volts reference.

The following are procedures for input scaling adjustments:

- 1. Place the system into the IC mode. (para 1.7.1)

- 2. Position both the Y ADDRESS and X ADDRESS switches to GND.

- Adjust the plotter or oscilloscope X and Y zero controls until plotter's pen or oscilloscope's dot is the the graph or display center.

- 5. Position the Y ADDRESS and X ADDRESS switches to -REF.

- Adjust the plotter or oscilloscope X and Y gain controls until the pen or dot is the pen or dot negative full scale deflection.

- 7. Position the Y ADDRESS and X ADDRESS switches to +REF.

### OPERATOR'S & MAINTENANCE MANUAL

- 8. Check the pen or dot. It should be the positive full scale deflection.

- 9. Repeat the procedures if necessary.

The readout instruments will either plot or display an amplifier output as a function of time or of another amplifier output, as selected by Y and X ADDRESS switch positions (para 1.5.) Regarding time functions, zero time begins at the negative full scale deflection and sweeps to positive full scale, where the positive full scale deflection equals the compute time period (para. 1.3.)

If the oscilloscope internal time base is used for the repetitive operation display, the fast time scale ratio of 400:1 must be considered: one computer time second equals 2.5 milliseconds real time.

#### 1.2 SETTING COEFFICIENT POTENTIOMETERS

Coefficients are set in IC mode (para 2.3) where a setting is displayed by the digital voltmeter and a selected potentiometer is adjusted until the desired setting is observed. Setting procedures are:

- 1. Place the system into the IC mode. (para 1.7.1)

- Complete all patching so that settings are made under their operating loads.

- 3. Position the DVM SELECTOR switch to POT.

- 4. Depress the pot set button adjacent to the potentiometer to be set and adjust the potentiometer knob until the desired setting is displayed.

- 1.2.1 Effects of Amplifier Overrange

An amplifier overrange will alter the setting of any pot patched to the overranged amplifier input. If the overload alarm appears when a pot set button is depressed, remove the overrange condition by patching overranged amplifier outputs directly to their summing junctions. Be sure to remove these patch cords prior to running the program.

#### 1.3 SETTING THE COMPUTE TIME PERIOD

The Compute Time Period is the time taken by the internal time base to sweep from minus to plus reference, the full scale X axis coordinate of plotted or displayed time response curves. It is adjustable from 10 to approximately 100 computer time seconds by the COMPUTE TIME control. Setting procedures are:

- 1. Place the system into the IC mode. (para 1.7.1)

- 2. Position the Y ADDRESS to TIME, the DVM SELECTOR switch to AMP.

- 3. Depress the pot set button adjacent to the COMPUTE TIME potentiometer and adjust the knob until the desired compute time period (displayed value times one hundred) is displayed.

## 1.4 DIGITAL VOLTMETER MEASUREMENTS OF AMPLIFIER OUTPUTS

To measure static values of amplifier outputs:

- 1. Position the DVM SELECTOR to the AMP position.

- Position the Y ADDRESS switch to the number of the amplifier output to be measured.

- 3. Read the display.

#### 1.5 SETTING INITIAL CONDITIONS

Each GP-10 integrator has an initial condition potentiometer and set up toggle switch. To set an initial condition:

- 1. Measure with the DMM the integrator output. (para 1.4)

- 2. Set the adjacent toggle switch to plus or minus.

- Adjust the potentiometer knob until the desired value is displayed.

#### 1.6 MEASUREMENT OF THE SUM OF INTEGRATOR INPUTS

In accordance with program static check requirements, to measure the sum of integrator inputs:

- Place the system into the IC mode. (para 1.7.1)

Patch the SJ jack of the integrator input to be measured to the SJ jack of an unused amplifier patched as a summer-inverter. The summer may require either a 1 or .1 feedback resistor depending upon the output resulting from the borrowed network.

- 3. Place the system into the HD mode. (para 1.7.2)

- 4. Measure the amplifier output. (para 1.4)

#### 1.7 MODE CONTROL

The following system integrator modes are controlled by depressing one of the four MODE CONTROL push buttons.

- 1.7.1 IC...Initial Condition Mode, initial condition values are applied to integrators. (para 1.5)

- 1.7.2 HD...Hold Mode, integrators hold values at the instant the hold mode logic is applied.

- 1.7.3 OP...Operate Mode, integrators are placed into a slow time run condition. (1:1 time scaling)

- 1.7.4 RO...Repetitive Operation Mode, integrators are placed into a high speed condition (400:1 time scaling) and alternately placed into the initial condition and operate modes so that repeated solutions are superimposed as a solid curves on an an oscilloscope display.

- \*Note: The OP (mode control) Bus originates at the MICROHYBRID I patch panel. Logic generated by the above operations is first directed to the OP and OP blue input MODE CTL jacks. To operate the system from these panel operation it is necessary to patch the blue and orange OP to OP jacks and HD to HD jacks together.

### 1.8 PROBLEM SOLUTION

The typical analysis of an analog computer simulation is to evaluate the response curves of dependent variables (ampliier outputs) as functions of the independent variable (time.)

To produce time response curves:

- 1. Y Axis... Position the Y ADDRESS to amplifier output that is to be the ordinate.

- 2. X Axis... Position the X ADDRESS switch to TIME, the abscissa. (The wiper of the Y ADDRESS switch is connected to the rear terminal Y OUTPUT.)

Oscilloscope Display:

3. Place the system into the repetitive operation mode. (para 1.7.4) The entire response curve is displayed.

XY Recorders:

- 3. Place the system into the initial condition mode. (para 1.7.1) All integrators are placed into an initial condition

- 4. Place the system into the operate mode. (para 1.7.3) All integrators are simultaneously placed into a run state and a plot of the response curve is drawn.

Evaluation of Time Response Curves Based on Physical Units

Y Axis...Where zero is the center co-ordinate, the full scale coordinates are equated to physical units by setting them equal to the amplifier output's scale factor. (The full scale estimated amplitude page 4

assigned to derive a program's scaled equations. An output in physical units equals the amplifier's normalized output value voltage output times the scale factor. (The normalized output assumes 10 volts reference to be unity and all outputs a ratio of the 10 volt maximum.)

X Axis...The full scale X axis co-ordinate is the compute time period in computer time units divided by the program's time scale factor.

Changing the Compute Time Period

If it is determined that the compute time period is either too long or short for convenient display or recording, the COMPUTE TIME control may be adjusted and a new compute time period established. A new compute time period does not affect the response, only the time period of the response. If a convenient readout is not obtainable with the range of compute time period selections, a new program time scale factor must be selected.

To produce dependent variables vs. dependent variable curves:

Plotting or displaying a variable vs. an other variable requires only that the X ADDRESS switch be positioned to the desired amplifier number. In such cases, zero shall be the center co-ordinate; the oscilloscope or plotter plus and minus full scale co-ordinate, like the Y axis scaling, shall be set equal to the amplifier output's amplitude scale factor.

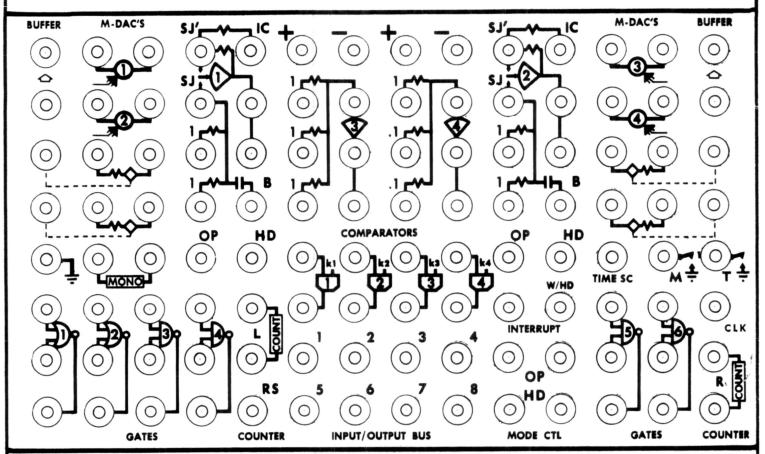

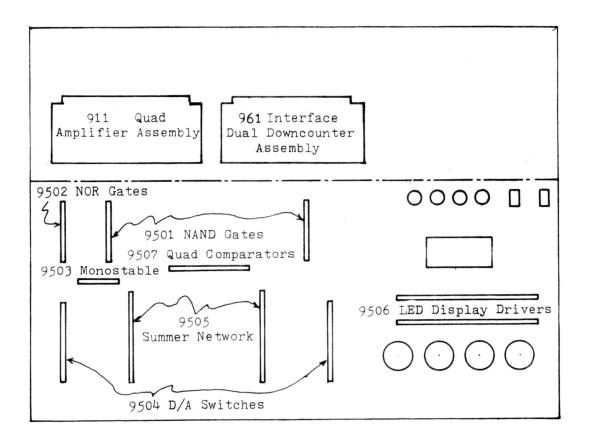

#### 1.9 MICROHYBRID I

#### 1.9.1 COMPARATOR BIAS ADJUSTMENTS

Each of the four COMPARATOR bias adjustments (knobs k1 thru k4) produces a voltage level that is summed with a patched input, producing when positive a comparator output of a logic 1, negative a logic 0. Bias levels are adjusted as follows through a range of -10 to +10 volts.

- 1. Apply a constant voltage equal to the desired bias level as the patch panel comparator input.

- 2. Adjust the COMPARATOR bias knob until a comparator state change is observed. To reach the transient position:

- If the output is a logic 0, turn the knob counterclockwise.

- If the output is a logic 1, turn the knob clockwise.

#### 1.9.2 LED INDICATORS

LED's are lit to indicate a logic 1 state.

#### 1.9.3 DIVIDE BY "N" COUNTER PRESET

Thumbwheel switches preset the two, two-decade downcounters. The left hand thumbwheels preset the L COUNTER; the right hand presets the R COUNTER. (While counting the output is a logic 0. When the counter register is zero, the output becomes a logic 1 and remains a logic 1 until the trailing edge of the next input pulse.)

The L COUNTER is preset when patched input R is a logic 0. The R COUNTER is preset when the blue input OP MODE CTL jack is a logic 0.

#### 1.9.4 OPERATOR CONTROL SWITCHES

- All pushbutton switches are a latched-up logic  $\mathbf{1}$ , a logic  $\mathbf{0}$  when depressed.

- The toggle switch is either a logic 1 or logic 0 as indicated on panel.

#### 1.a SLAVING TWO OR UNITS TOGETHER

When problem requirements exceed the capacity of one LGP-20, two or more units may be slaved into a single operating system.

- 1. Designate a unit to be the master; others shall then be slaves to the master.

- 2. Connect a slave cable to the SLAVE connectors of master and slave units.

- 3. Patch each unit and the interconnections between units.

- 4. Depress the OP mode control push button(s) on unit(s) designated as the slave(s.)

- 5. Run the total system from the master.

#### 1.b OVERRANGE

When any of the GP-10 (upper or lower) operational amplifiers exceed either plus or minus reference, the control panel OVERRANGE light will light. (The actual overrange threshold is normally set to about 1.05. See the 970 Overload Indicator circuit description for adjustment procedures.)

In addition to the control panel OVERRANGE alarm, each of the GP-10 patch panels has an LED alarm located in the lower right hand corner.

To determine the amplifier (s) in an overrange condition, first check in which GP-10 the overrange is occurring, then sequentially step through the Y ADDRESS switch and observe amplifier output values. (para 1.4)

#### 1.c POWER

The AC power switch is located at the rear of the unit under the AC power receptacle. A 'power on' condition is apparent by the appearance of the digital voltmeter display.

page 6

## 2. OPERATOR FUNCTIONS

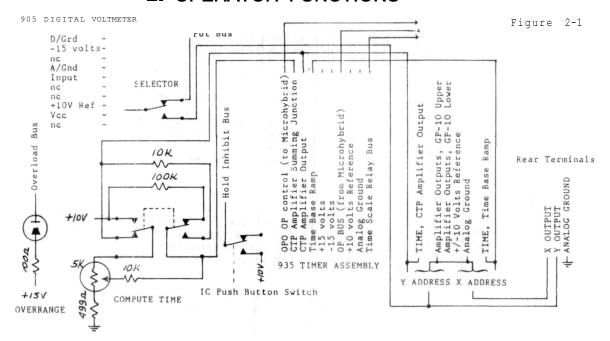

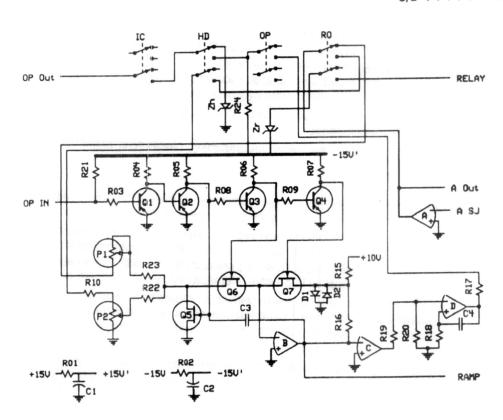

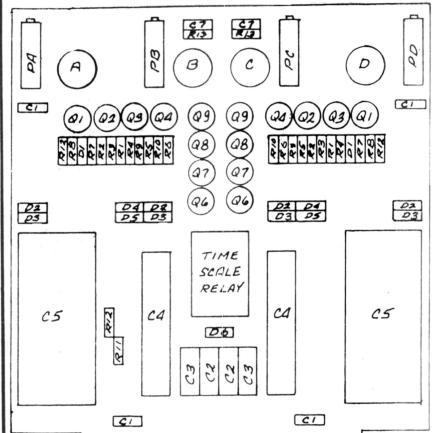

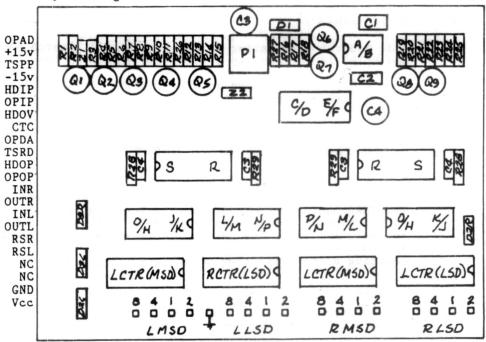

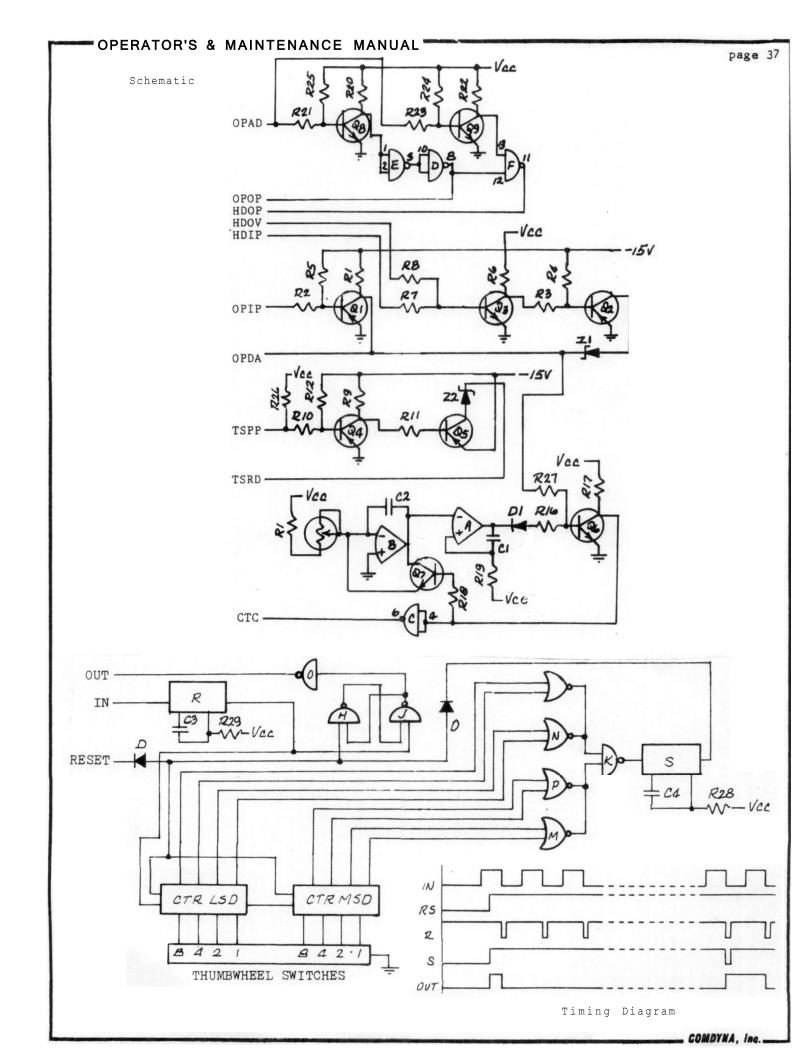

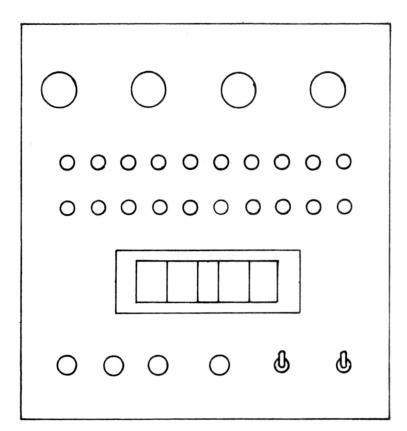

Figure 2-1 is a schematic of operator functions. Descriptions of the individual operations are described in the following:

#### 2.1 Y ADDRESS

The Y ADDRESS switch is an 24 position, single pole rotary switch. Contacts 1-8 are connected to lower GP-10 amplifier outputs 1-8, 9-16 are connected to upper GP-10 amplifier outputs 1-8, 17-20 are connected to Microhybrid I amplifiers 1-4, 21 is ground, 22 is -10V, 23 is +10V, 24 is the CTP amplifier output which is the input to the time base integrator output. The wiper is connected to the rear terminal Y OUTPUT and DVM SELECTOR toggle switch, AMP contact.

## 2.2 X ADDRESS

The X ADDRESS switch is the same as the Y ADDRESS except that the TIME position is the time baseramp. The wiper is connected to the rear term in al X OUTPUT.

#### 2.3 MODE CONTROL

The following system integrator modes are controlled with the four mode control push buttons.

- 2.3.1 Initial Condition...Depression of the IC push button pulls the OP bus to ground for reset of system integrators.

- 2.3.2 Hold...Depression of the HD push buttons pulls the OP bus to a hold mode control voltage level (approximately -2 volts) for placement of system integrators into a hold mode condition.

- 2.3.3 Operate...Depression of the OP push button releases the OP bus to an operate mode control level (-5 to -15 volts) for placement of system integrators into a slow time, operate condition.

- 2.3.4 Repetitive Operation...Depression of the RO push button places the Time Scale Relay bus into a de-energized state and connects the OP bus to the repetitive operation timing unit mode control.

- 2.3.5 OP Bus...The system mode control bus, originates at the Microhybrid. Above described operations are changed to TTL logic terminated at the Microhybrid orange OP and HD jacks. For these operations to produce the OP Bus it is necessary to patch the orange to the blue inputs, OP to OP and HD to HD.

#### 2.4 COMPUTE TIME

The COMPUTE TIME control consists of a coefficient potentiometer and a double pole, double throw push button switch that serves to program the CTP amplifier. In a normal operating condition the coefficient adjusts the time base integrator within a range of -10 to -1 volts which produces a compute time period of 10 to 100 computer time seconds.

Depression of the button control rearranges the input and feedback resistor network to produce an output that is an inverse of the released condition.

In the released position, +10 volts is applied through the COMPUTE TIME control (100K ohms) and a series 10K ohm resistor to the CTP amplifier summing junction. A 10K ohm resistor is the feedback. Therefore:

$CTP = -10/(CT + 10) \times 10 \text{ volts}.$

In the depressed position, +10 volts is applied through a 100K ohm resistor to the CTP summing junction. The COMPUTE TIME control and 10K ohm resistor are the feedback. Therefore:

$CTP = -(CT + 10)/100 \times 10 \text{ volts.}$

The CTP amplifier output in the depressed position is one tenth the reciprocal of its value in the released position. As the CTP output is the input to the time base integrator, its reciprocal is an indicator of the compute time period.

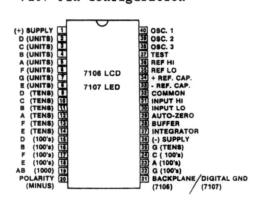

#### 2.5 DIGITAL VOLTMETER

The digital voltmeter is an +/-10 volts input, 3 1/2 digit resolution, where the decimal point is positioned so that a 10V measurement is displayed as 1.000, in accordance with normalized analog computer scaling methods.

An input to the digital voltmeter is either the Pot Bus (POT) or Y ADDRESS switch wiper (AMP) as determined by the SELECTOR switch position.

- 2.5.1 Pot Bus Function...When the button adjacent to any system coefficient potentiometer is depressed, the patch panel input to the top of the pot is replaced by +10V reference and the wiper is connected to the Pot Bus.

- 2.5.2 Hold Inhibit...In the IC mode (para 1.7.1) the Hold Inhibit Bus is switched to +10V to force the hold switches of all integrators to conduct. Without the hold inhibit feature the hold switch shuts off and thereby isolates the input resistor network. As coefficient potentiometers must be set with their programmed resistor loads, it is necessary that the hold switches be on so that the network summing junctions conduct to ground through the shunt FETs. (See 911-3 Quad Amplifier Assembly)

## 2.6 OVERRANGE ALARM

The panel LED anode is connected to Vcc through a 100 ohm resistor. The cathode is a common to each of the two GP-10 panel LED alarms. Each of these cathodes is pulled to ground when a GP-10 amplifier is in an overrange condition. (See 970-1 Overload Indicator)

## 2.9 REAR TERMINATIONS

2.9.1 Binding Posts...The three binding posts are identified as Y OUTPUT, ground and X OUTPUT and are terminations for the X and Y address switches wipers and signal ground. (para 2.1 and 2.2.

2.9.2 TRUNKS...Trunks are terminated in three 25 pin type D data connectors, listed below. Facing the rear of the unit, pin 1 is upper row left, pin 14 is lower row left.

|                                                                           | TOP                                                                                  | MIDDLE                                                               | BOTTOM                                                  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------|

| 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>10.<br>11.<br>12.   | nc +10V Reference -10V Reference Agnd nc OP Bus nc TS Relay Bus nc Chassis ground nc | Agnd MO3 TR7 (upper GP-10) Agnd MO2 TR6 Agnd TR5 TR5 Agnd MI4 TR4 nc | nc nc nc 1/04 1/02 1/08 1/06 nc nc nc nc                |

| 14.<br>15.<br>16.<br>17.<br>18.<br>19.<br>20.<br>21.<br>22.<br>23.<br>24. | nc<br>nc<br>nc<br>TR1 (lower GP-10)<br>TR2<br>TR3<br>TR4<br>TR5<br>TR6<br>TR7        | TR8 Agnd MI3 TR3 Agnd MI2 TR2 Agnd MI1 TR1 Agnd MO4                  | Interrupt RESET STOP GO I/03 I/01 I/07 I/05 nc nc nc nc |

## notes:

- 1. Agnd is analog ground; DGnd is digital ground.

- 2. TR refers to GP-10 trunks. Trunks from the lower GP-10 are found in the top connector, the upper GP-10 in middle connector.

- MD refers to a Microhybrid MDAC output jack. MI refers to a MICROHYBRID MDAC input jack.

- 4. I/O refers to the MICROHYBRID I/O BUS jacks.

- 5. Interrupt is the MICROHYBRID INTERRUPT jack.

- 6. RESET, STOP and GO are connections to the latch-up push button switches so marked on the MICROHYBRID I panel.

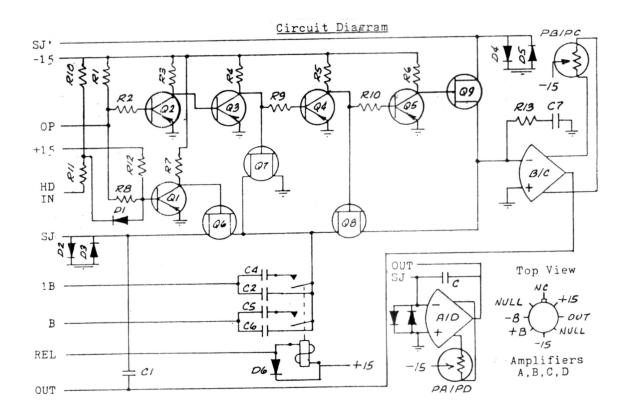

# **GP-10 ANALOG COMPUTING UNIT**

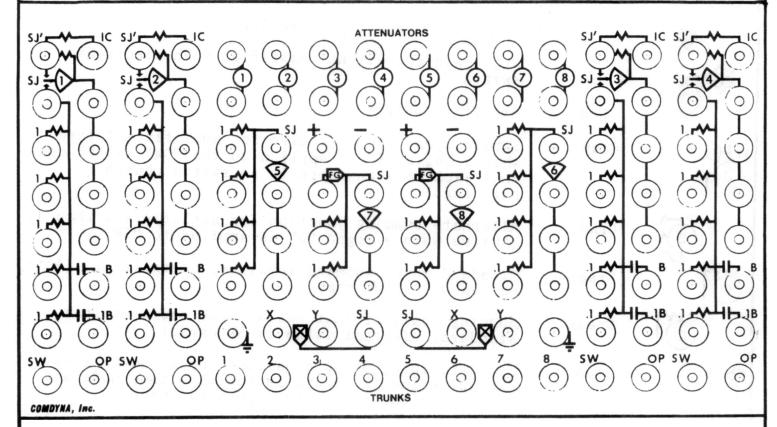

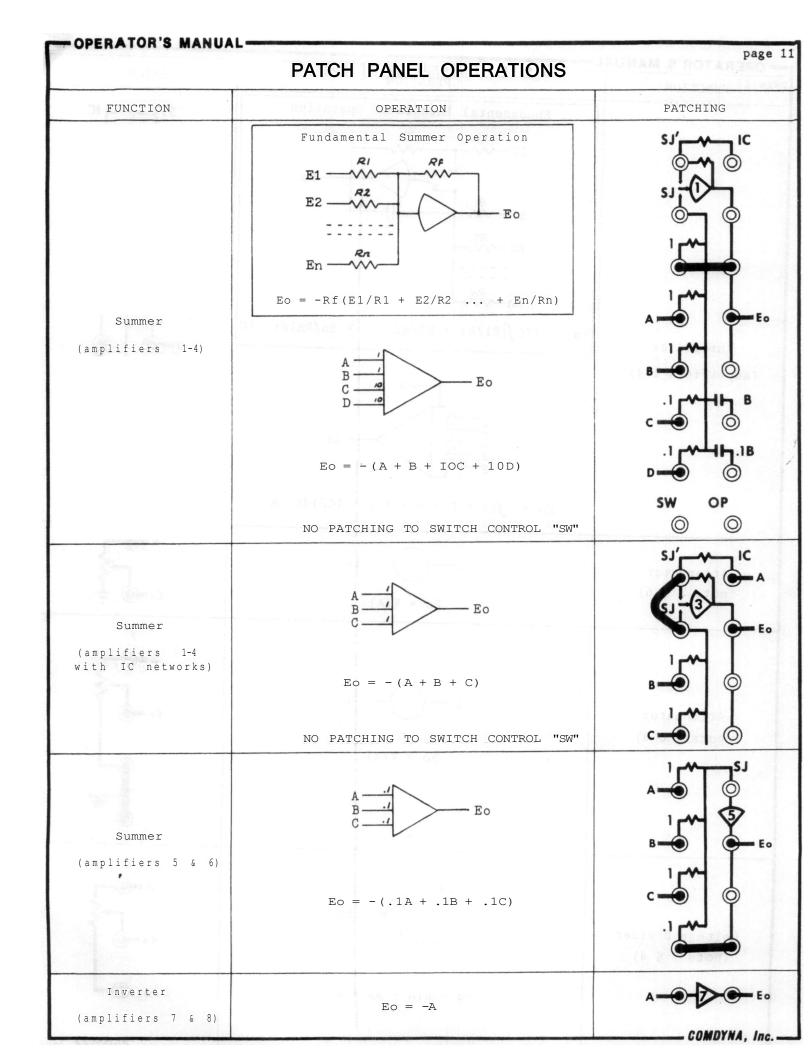

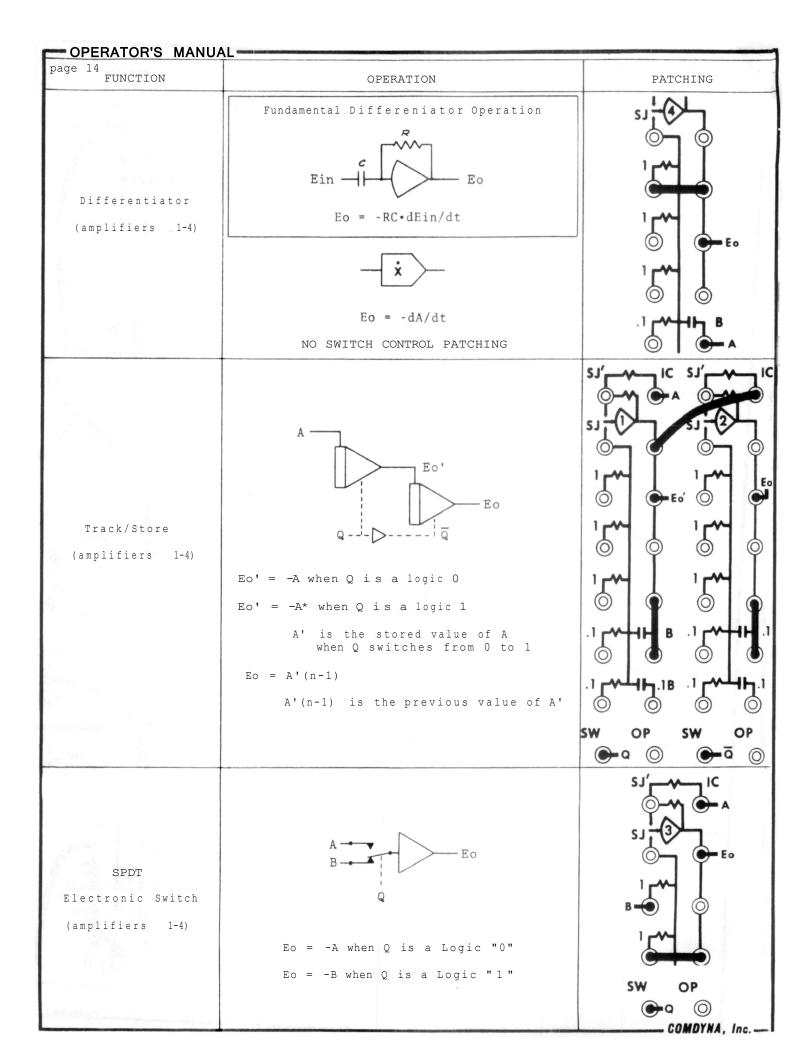

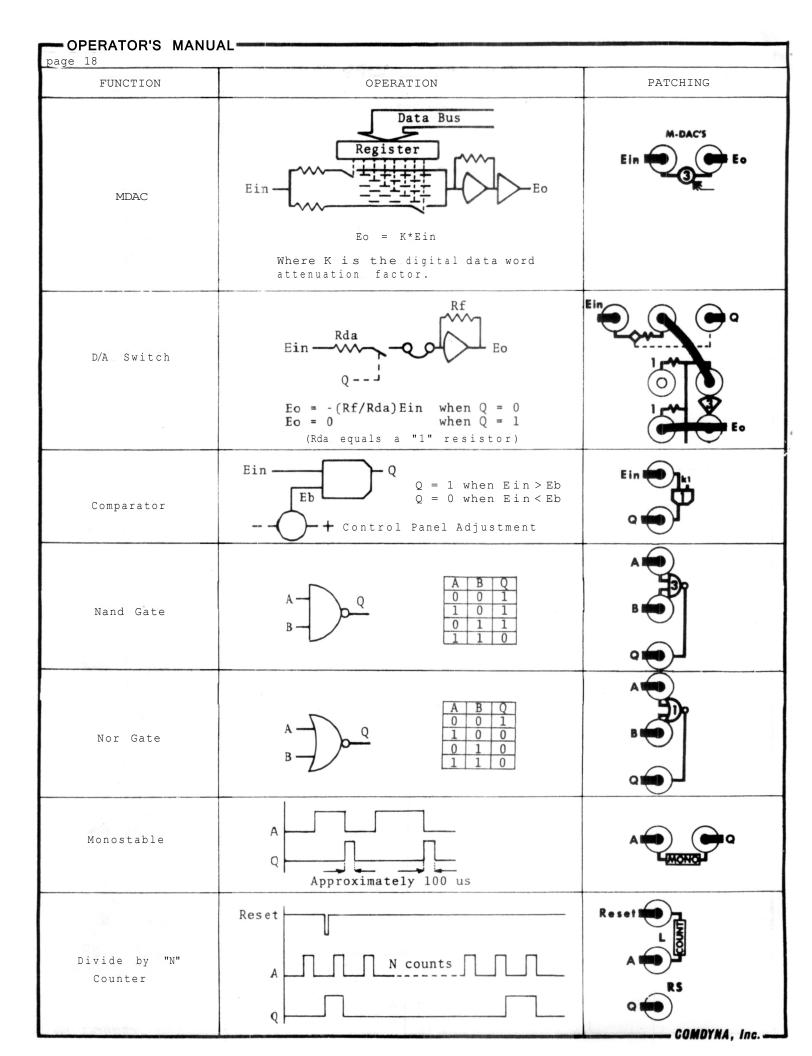

Patch panel graphics represent networks as they are applied in normal analog computer programming. All amplifiers may be used as summers or high gain operational amplifiers; amplifiers 1 thru 4 have electronic switch networks and may be programmed as integrators, track/store amplifiers and single pole, double throw electronic switches. Initial Condition Attenuator wipers are connected to the "IC" inputs for entering manually set constants. Eight Attenuators have their inputs and wipers terminated at the patch panel. Multiplier networks have current outputs; with one amplifier each may be used as a multiplier, divider, squarer or square root extractor. Eight trunk jacks may be used to route external inputs and outputs. The two "FG" trunks that are connected to amplifiers 7 and 8 are reserved for diode function generator inputs.

The following is a description of patch panel symbols:

| SYMBOL   | COLOR CODE | DESCRIPTION                                                                                          |  |  |  |  |

|----------|------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| <b>6</b> | Orange     | Positive reference, considered unity, 1.000, for formalized programming. (Actual value is 10 volts.) |  |  |  |  |

| 0        | Yellow     | Negative reference.                                                                                  |  |  |  |  |

| (O)      | Black      | Analog Signal Ground.                                                                                |  |  |  |  |

|          | Yellow     | Manual attenuator input.                                                                             |  |  |  |  |

| 4 0      | Yellow     | Manual attenuator wiper or output.                                                                   |  |  |  |  |

| TRUNKS   | White      | Trunk lines. Routing determined by user.                                                             |  |  |  |  |

| OPER/                                          | ATOR'S & MAIN | TENANCE MANUAL                                                                                                                                                                                                                                                                                               |

|------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| page 10<br>SYMBOL                              | COLOR CODE    | DESCRIPTION                                                                                                                                                                                                                                                                                                  |

| ₩ 🕉                                            |               | High gain operational amplifier.                                                                                                                                                                                                                                                                             |

| <b>ED</b>                                      |               | High gain operational amplifier with electronic switch.                                                                                                                                                                                                                                                      |

|                                                | Red           | Amplifier output.                                                                                                                                                                                                                                                                                            |

| 3.4.V                                          | Gray          | Summing junction. (Active for amplifiers 1 thru 4 when a logic "1" is applied to the "SW" switch control jack or when there is no switch control patching.)                                                                                                                                                  |

| 21,00                                          | Gray          | Alternate summing junction for amplifiers 1 thru 4. (Active when a logic "0" is applied to "SW.")                                                                                                                                                                                                            |

| 6                                              | Green         | Standard input summing resistor, normalized. (Actual value is 50K ohms.)                                                                                                                                                                                                                                     |

| 6                                              | Green         | Summing resistor that has a value one tenth the standard. (Actual value is 5K ohms.)                                                                                                                                                                                                                         |

| (O)                                            | Blue          | Standard integrating capacitor input, normalized. (Actual value is 20 ufd in the slow time mode and .05 ufd in the repetitive operation mode.)                                                                                                                                                               |

| 4b 18                                          | Blue          | Integrating capacitor that has a value equal to one tenth the standard. (Actual value is 2 ufd in the slow time mode and .005 ufd in the rep. op. mode.)                                                                                                                                                     |

| 5 <b>M</b> (0)                                 | Green         | Resistor network. Amplifier becomes an inverter when SJ' is active. When SJ is active, amplifier may be a summer by patching SJ and SJ' together. "IC" jack is the normal integrator initial con-                                                                                                            |

| E3L                                            |               | dition input as it is connected to the associated Initial Condition Attenuator wiper. (Value of resistors is 50K ohms.)                                                                                                                                                                                      |

| ;w<br>⊙                                        | White         | Electronic switch control input. With a logic "0" (ground or positive voltage) the SJ' summing junction is active and SJ shuts off. With a logic "1" (-5 thru -15 volts) SJ is active and SJ' shuts off. With "HD" logic (-2 thru -3 volts) SJ' shuts off, the SJ summing junction is active but the summing |

| OP<br>O,                                       | White         | resistor network is disconnected.  The system's operate bus; provides integrator mode control logic as selected by the operator.                                                                                                                                                                             |

| (a) (b) (c) (c) (c) (c) (c) (c) (c) (c) (c) (c | Brown         | Multiplier network. "X" and "Y" are inputs.                                                                                                                                                                                                                                                                  |

| sı<br>Sı                                       | Gray          | Multiplier output, a current that is proportional to the product of inputs "X" and "Y."                                                                                                                                                                                                                      |

|                                                | Brown         | Trunks allocated as function generator inputs to amplifiers 7 and 8.                                                                                                                                                                                                                                         |

GOMDYNA, Inc.

| page 12 FUNCTION                | OPERATION                                                                                                                                                           | PATCHING                                  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Integrator (amplifiers 1-4)     | Fundamental Integrator Operation  IC $Ric$ $Ric$ $Eo$ $Eo$ $E1$ $E2$ $E2$ $E2$ $E3$ $E4$ $E5$ $E5$ $E6$ $E7$ $E7$ $E7$ $E8$ $E9$ $E9$ $E9$ $E9$ $E9$ $E9$ $E9$ $E9$ | SW OP                                     |

| Attenuator (pots 1 - 6)         | $A \longrightarrow Eo$ $Eo = K(A)$                                                                                                                                  | A — — — — — — — — — — — — — — — — — — —   |

| Attenuator<br>(pots 7 & 8)      | A — Eo  Eo = K(A)                                                                                                                                                   | A - 0 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 |

| Voltage Divider<br>(pots 7 & 8) | $ \begin{array}{c} A \\ B \end{array} $ $ EO = K(A - B) + B $                                                                                                       | A                                         |

| FUNCTION    | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PATCHING page                           |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|             | Fundamental Multiplier Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | © \$1                                   |

|             | X Z Z Eo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |

| Multiplier  | Eo = -(X*Y)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )   P = 0                               |

|             | $ \begin{array}{ccc} A & & & & & & \\ B & & & & & & \\ Eo & = & -(A * B) \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 <b>L</b>                              |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A O                                     |

| 2           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                       |

| Divider     | B Eo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .1 [ ]                                  |

| BIVIGEI     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ا لسار.                                 |

|             | Eo = -(A/B) $A > 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B → X                                   |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I Landson                               |

| Squarer     | A - X2 Eo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | THE P                                   |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) |

|             | $Eo = -A^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A-CX                                    |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 <b>L</b> ~ L S 1                      |

|             | A - V Eo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A-0                                     |